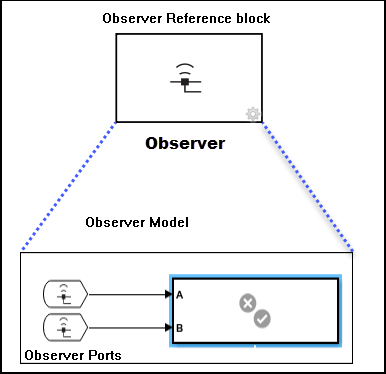

Можно изолировать логику верификации в модели при помощи Observer Reference блоков. Блоки Observer Reference служат идеальным кандидатом, когда вы хотите сохранить логику верификации отдельно от вашей модели проекта. Когда вы используете Observer Reference (Simulink Test), можно вносить изменения в модель Observer, не меняя модели проекта. Использование Observer Reference блоков может помочь вам задать свойства или требования на ранних этапах проектирования модели или в нескольких проектах модели. Блок Observer Reference также позволяет вам:

Моделируйте требования проект как свойства и доказывайте их с помощью Simulink® Design Verifier™.

Установите результаты базовой линии на основе захваченного выхода и обнаружите регрессии модели.

Сгенерируйте тесты для требований функционального проекта с помощью пользовательских целей тестирования.

Дважды кликните блок Observer Reference, чтобы открыть модель Observer. Observer Reference блоки могут находиться только на верхнем уровне системной модели и не иметь входных портов. Для получения дополнительной информации смотрите Доступ к данным Моделям Беспроводной при Помощи Наблюдателей (Simulink Test).

При разработке пользовательских целей целей верификации вместо блока Observer Reference может использоваться блок Verification Subsystem. Блок Observer Reference ссылается на отдельную модель верификации, называемую моделью Observer, которую вы используете, чтобы проверить свою системную модель. Преобразование блока Verification Subsystem в блок Observer Reference может объявить системную модель. Чтобы преобразовать блок Verification Subsystem в блок Observer Reference, щелкните правой кнопкой мыши подсистему верификации и выберите Observers > Move selected block to Observer > New Observer. Эта операция не может быть отменена. Это действие добавляет блок Observer Reference к вашей системной модели и открывает модель Observer. Вы должны сохранить модель Observer в папке с возможностью записи на MATLAB® путь.

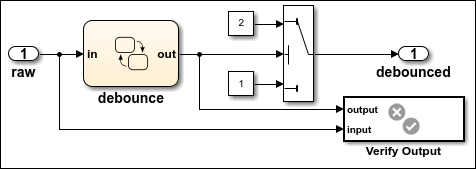

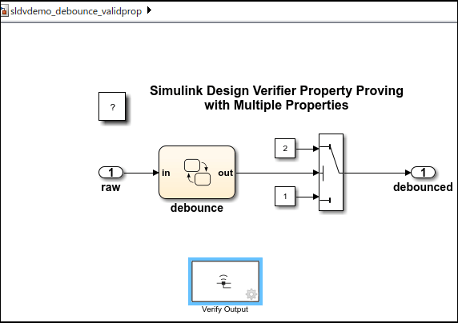

Рассмотрим случай, когда модель sldvdemo_debounce_validprop содержит блок Verification Subsystem Verify Output.

Преобразовывая подсистему в блок Observer Reference, вы удаляете сигналы, которые соединяют подсистему с системной моделью, сохраняя при этом возможность тестирования целостности системы.

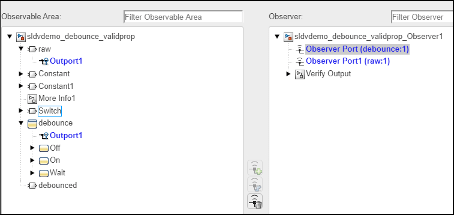

Эти два сигнала, debounce и raw, автоматически сопоставляются с двумя блоками Observer Port в модели Observer, sldvdemo_debounce_validprop_Observer1.

Можно проверить свойства sldvdemo_debounce_validprop без внесения каких-либо изменений в модель проекта.

Если ваша модель включает блок Observer Reference, отчет анализа Simulink Design Verifier показывает информацию о свойстве и тесте генерации для блоков Ссылки Observer в подразделе Observer Model(s) и информацию о модели проекта в подразделе Design Model. Для получения дополнительной информации см. раздел «Отчеты Simulink Design Verifier».

Simulink Design Verifier не поддерживает:

Observer Reference блоки, которые наблюдают сложные сигналы, сигналы шины или данные Stateflow.

Модели наблюдателя, которые включают Model Referenced блоков.

Применение правил замены блоков к моделям Observer

Модель наблюдателя, которая запускается с другой базовой скоростью, чем модель проекта.

Настройка параметров внутри модели Observer.

Отладка нарушений свойств внутри модели Observer с помощью Model Slicer.

Генерация тестов для кода, сгенерированного Embedded Coder® для моделей, которые содержат блоки Observer Reference.

Simulink Design Verifier не анализирует логику внутри моделей Observer для ошибки проектирования и анализа обнаружения мертвой логики.

Анализ Simulink Design Verifier возвращает ошибку, когда:

Вы анализируете автономных наблюдателей.

Вы выполняете экстракцию подсистемы на блоке Observer Reference.

Модель Observer использует настройки решателя с переменным шагом.

Используйте Ссылочный Блок Наблюдателя для Генерации Теста | Используйте Ссылку Блоков Observer для анализа свойств | Порт наблюдателя (Simulink Test) | Observer Reference (Simulink Test)