Приложение SoC состоит из одного или нескольких алгоритмов. Когда алгоритм передает данные другому алгоритму, данные представлены как сигнальная линия в Simulink®. Для поведенческих моделей передача данных происходит мгновенно.

Эта схема показывает поведенческую модель datapath между двумя алгоритмами.

В физическом мире алгоритмы могут быть на двух отдельных устройствах, и передача данных не происходит мгновенно. Кроме того, алгоритмы могут запускаться с различными скоростями и, следовательно, требуют буферизации и управления логикой для квитирования. Для примера, простое квитирование типа «данные действительны» от производителя данных и «готовы принять данные» от потребителя служит логикой управления.

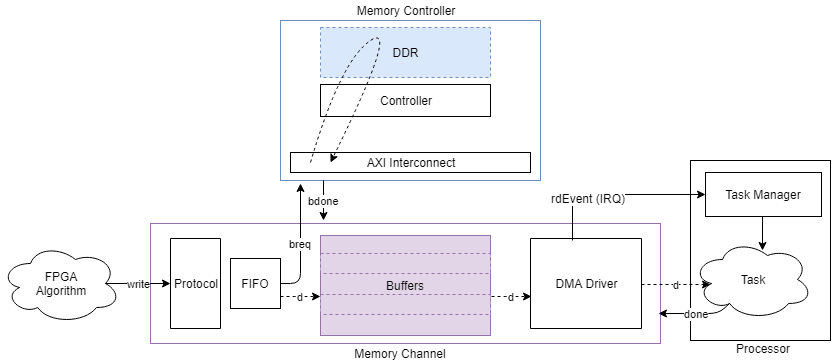

Если один элемент обработки выполняется в FPGA или ASIC, а следующий элемент обработки выполняется во встраиваемом процессоре, то простая сигнальная линия представляет больше, чем просто сложное аппаратное средство передачи данных. Передача данных также представляет обработчик прерывания процессора, планировщик задач операционной системы и стек драйверов программного обеспечения.

В SoC Blockset™ вы данными моделями передачи и протоколы квитирования через общую память. Используйте блок Memory Channel для внешней памяти или блок Register Channel для регистров.

Блок Memory Channel представляет абстракцию к комплексному datapath через внешнюю память и поддерживает различные протоколы квитирования. Это облегчает уточнение связи между элементами обработки от мгновенного провода без протокола до соединения с полным прямым доступом к памяти (DMA) между процессором и FPGA.

Путем добавления блока Memory Channel можно смоделировать перемещение данных из одной части алгоритма в другую.

Блок предоставляет модель коммуникационного конвейера. Канал также обеспечивает интерфейс сигнализации.

Протокол интерфейса зависит от того, где выполняется обработка. Алгоритм FPGA или ASIC может выполнять передачу данных с помощью стандартных протоколов, таких как AXI4-Stream или AXI4. Встроенный алгоритм центральный процессор может использовать интерфейс драйвера, экспортированный в пользовательское пространство.

Этот рисунок показывает модель datapath от потоковых данных алгоритма FPGA к алгоритму процессора.

Другие варианты выбора типа Memory Channel моделируют дополнительные общие папки данных через внешнюю память. Для получения дополнительной информации об Memory Channel строений см. Memory Channel.

Средство записи и чтения подключаются к памяти и запрашивают доступ к внешней памяти от контроллера памяти. Для получения дополнительной информации о блоке Memory Controller см. Memory Controller.

Блок Register Channel представляет сериализацию процессора, считываемого или записываемого через общую шину строения, такую как AXI-Lite.

Блок Register Channel предоставляет модель синхронизации для передачи значений регистров между процессором и аппаратными алгоритмами через общую шину строения. Используйте этот блок, когда процессор записывает команду или реестр строения или когда процессор читает регистр состояния.

Memory Channel | Register Channel