Арбитражные транзакции памяти для одного или нескольких блоков Memory Channel

SoC Blockset/Память

Блок Memory Controller арбитрирует между мастерами и предоставляет им уникальный доступ к общей памяти. Сконфигурируйте этот блок для поддержки нескольких каналов с различными арбитражными протоколами. Блок Memory Controller также инструментализируется для регистрации и отображения данных о эффективности, что позволяет вам отлаживать и понимать эффективность вашей системы во время симуляции.

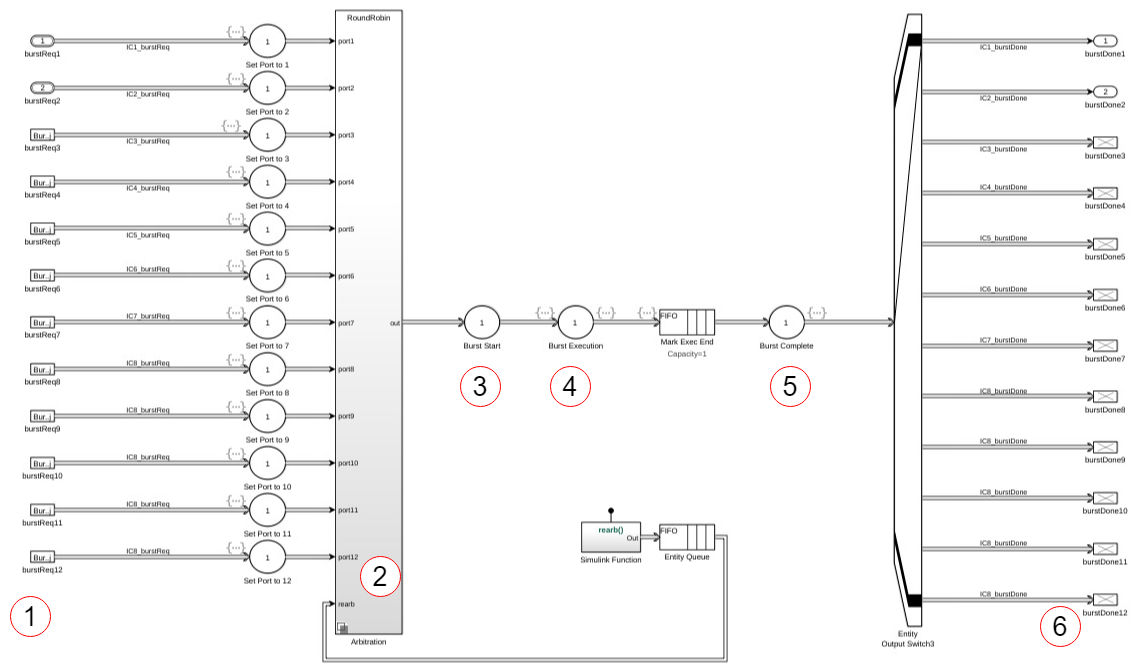

На следующем изображении показана реализация блока Memory Controller.

Цифры в изображении представляют различные стадии задержки блока.

В блок поступает пакетный запрос.

Запрос может быть отложен арбитражем до тех пор, пока ему не будет предоставлен доступ к bus. установить арбитражную политику в арбитраже Interconnect.

Если ваша модель требует дополнительной задержки перед началом первой передачи, установите это значение в Request to first transfer (в часах).

Задержка выполнения пакета вычисляется размером пакета, шириной данных, тактовой частотой и значением снижения полосы пропускания (%).

Если ваша модель требует задержки от завершения пакета до выдачи пакетного ответа каналу, установите это значение в поле Последняя передача в транзакцию завершена (в часах).

Контроллер памяти имеет внутреннее состояние, которое видно при использовании Logic Analyzer для просмотра метрик симуляции и выполнения. Значения состояния:

BurstRequest: Запрос пакета поступает в блок.

BurstExecuting: Пакет выполняется.

BurstDone: Пакет выполнен.

BurstComplete: Пакет завершен, и сигнал burstDone отправляется в ведущее устройство.

Для получения информации о визуализации задержек контроллера памяти смотрите Графики задержки контроллера памяти.

Когда Interconnect arbitration установлено на Round Robin, модель не поддерживает симуляции шага. Для получения дополнительной информации о шаге симуляции, см. Simulation Stepper.

Memory Channel | Memory Traffic Generator | Register Channel