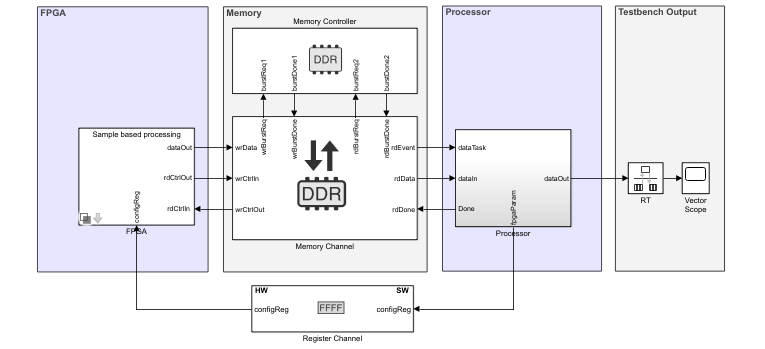

Модель SoC Blockset™ состоит из модели верхней части, которая включает, по крайней мере, один из этих образцов модели.

Образец модели FPGA представляет часть FPGA однокристального устройства. Верхняя модель может включать в себя не более одной образцы модели FPGA. Для получения информации о том, как настроить образец модели FPGA, смотрите Логику пользователя на FPGA.

Образец модели процессора представляет процессорную часть однокристального устройства. Верхняя часть может включать одни или несколько образцов модели процессора. Для получения информации о том, как настроить образец модели процессора, смотрите Программное обеспечение и Управление задачами на процессоре.

Процессор и подсистемы FPGA взаимодействуют через Memory Channel, Register Channel или Interrupt Channel блок.

В сложение к FPGA и процессорным образцам модели модель верхней части может включать дополнительные блоки SoC Blockset, такие как перечисленные здесь блоки, для моделирования интерфейсов и испытательного стенда компонентов.

На следующем изображении показана модель SoC Blockset с образцом модели FPGA, образцом модели процессора, осуществляющей связь по каналу памяти.

Пример модели SoC Blockset см. в разделе Потоковая передача данных с оборудования на программное обеспечение.

SoC Blockset предоставляет шаблоны проектов для распространенных случаев использования SoC. Используйте их как начальная точка для своего проекта.