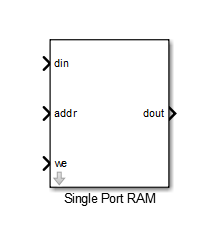

Один порт RAM

HDL Coder / RAM HDL

Модели RAM блока Single Port RAM, который поддерживает последовательные операции чтения и операции записи.

Если вы хотите к модели RAM, которая поддерживает одновременные операции чтения и операции записи, используйте Dual Port RAM или Simple Dual Port RAM.

Ширина адресного бита. Минимальная битная ширина равняется 2, и максимальная битная ширина равняется 29. Значение по умолчанию равняется 8.

Управляет выходными данными, dout, во время доступа для записи.

New data (значение по умолчанию): Во время записи новые данные появляются в выходном порту, dout.

Old data: Во время записи старые данные появляются в выходном порту, dout.

Блок имеет следующие порты:

dinВвод данных. Данные могут иметь любую ширину. Это наследовало ширину и тип данных от входного сигнала.

Тип данных: скалярная фиксированная точка, целое число или комплекс

addrЗапишите адрес.

Тип данных: скалярное беззнаковое целое (uintN) или фиксированная точка без знака (ufixN) с дробной длиной 0

weРазрешение записи.

Тип данных: Boolean

doutВыходные данные от адреса, addr.