Используя HDL Workflow Advisor, можно сгенерировать пользовательское ядро IP из модели или алгоритма. Сгенерированное ядро IP является с обеспечением совместного доступа и допускающим повторное использование. Можно интегрировать его с большим проектом путем добавления его в среде интегрирования встраиваемой системы, такой как Intel® Qsys, Xilinx® EDK или интегратор IP Xilinx.

Чтобы изучить, как сгенерировать пользовательское ядро IP, см.:

Можно сгенерировать ядро IP:

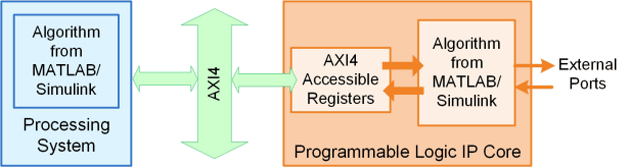

С интерфейсом AXI4 или AXI4-Lite.

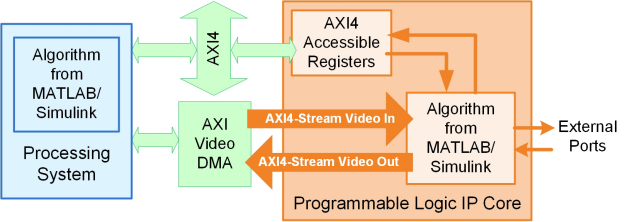

С интерфейсом AXI4 или AXI4-Lite и AXI4-потоковыми Видеоинтерфейсами.

Без любого AXI4 или AXI4-облегченных интерфейсов. Чтобы узнать больше, смотрите, Генерируют Независимое от Совета Ядро IP HDL из Модели Simulink.

Алгоритм из MATLAB и блока Simulink представляет ваш DUT. HDL Coder™ генерирует остальную часть ядра IP на основе ваших настроек интерфейса целевой платформы и процессора или режима синхронизации FPGA.

Можно сопоставить каждый порт в DUT к одному из этих интерфейсов целевой платформы в ядре IP:

AXI4-облегченный: Используйте этот интерфейс для регистров управления доступом или для легкой передачи данных. HDL Coder генерирует регистры с отображенной памятью и выделяет смещения адреса для портов.

AXI4: Используйте этот интерфейс, чтобы соединить с компонентами ту пакетную передачу данных поддержки. HDL Coder генерирует регистры с отображенной памятью и выделяет смещения адреса для портов. В сгенерированном ядре IP HDL у вас может быть любой интерфейс AXI4 или AXI4-Lite, но не оба интерфейса.

AXI4-потоковое Видео: Используйте этот интерфейс, чтобы отправить или получить 32-битный скалярный поток видеоданных.

Внешние порты: Используйте внешние порты, чтобы соединить с FPGA внешние контакты IO или с другими ядрами IP с внешними портами.

Сбор данных FPGA - JTAG: Используйте Сбор данных FPGA по интерфейсу JTAG, чтобы наблюдать сигналы тестовой точки и сигналы в выходных портах DUT, в то время как ваш проект работает на FPGA. Для примера маркировки внутренних сигналов как тестовые точки смотрите, что Ядро IP Отладки Использует Сбор данных FPGA. Для получения дополнительной информации о собирании данных смотрите Рабочий процесс Сбора данных (HDL Verifier).

Примечание

Чтобы использовать этот интерфейс, необходимо загрузить пакет аппаратной поддержки для платы FPGA. Смотрите Пакет поддержки плат FPGA Загрузки (HDL Verifier).

Чтобы узнать больше о AXI4, AXI4-облегченном, и AXI4-потоковые протоколы Видео, обращаются к вашей документации целевого компьютера.

HDL Coder генерирует логику синхронизации в ядре IP на основе процессора и режима синхронизации FPGA, который вы выбираете.

При генерации пользовательского ядра IP они процессор и опции синхронизации FPGA доступны:

Free running (значение по умолчанию)

Coprocessing – blocking

Чтобы узнать больше, смотрите Синхронизация FPGA и Процессор.

После того, как вы сгенерируете пользовательское ядро IP, файлы ядра IP находятся в ipcore папка в вашей папке проекта. В HDL Workflow Advisor можно просмотреть имя папки ядра IP в поле IP core folder HDL Code Generation> задача Generate RTL Code and IP Core.

Папка ядра IP содержит:

Файлы определения ядра IP.

Исходные файлы HDL (.vhd или .v).

Заголовочный файл C с таблицей адресов регистра.

(Необязательно) отчет HTML с инструкциями для использования ядра и интеграции ядра IP в вашем проекте встраиваемой системы.

Когда вы используете ограничения мультивелосипедной дорожки, чтобы удовлетворить требования синхронизации, HDL Coder генерирует ограничительный файл формата XDC (.xdc) для рабочего процесса Xilinx и формата SDC (.sdc) для рабочего процесса Intel.

Рабочий процесс Генерации Ядра IP не поддерживает:

Набор RAM Architecture к Generic RAM without clock enable.

Используя различные часы для ядра IP и интерфейса AXI. IPCore_Clk и AXILite_ACLK должно быть синхронно и связан с тем же источником часов. IPCore_RESETN и AXILite_ARESETN должен быть соединен с тем же источником сброса. Смотрите Синхронизацию Глобального Сигнала Сброса к Области Часов Ядра IP.