Когда вы открываете HDL Workflow Advisor и запускаете IP Core Generation рабочий процесс для вашего Simulink® модель, можно задать типовой Xilinx® платформа или типовой Intel® платформа. Рабочий процесс затем генерирует типовое ядро IP, которое можно интегрировать в любую целевую платформу по вашему выбору. Для интегрирования ядра IP задайте и укажите пользовательский исходный проект для своей требуемой платы при помощи hdlcoder.ReferenceDesign класс. Чтобы узнать больше, см.:

Сгенерировать независимое от платы пользовательское ядро IP, чтобы использовать в среде интегрирования встраиваемой системы, такой как Intel Qsys, Xilinx EDK или Интегратор IP Xilinx:

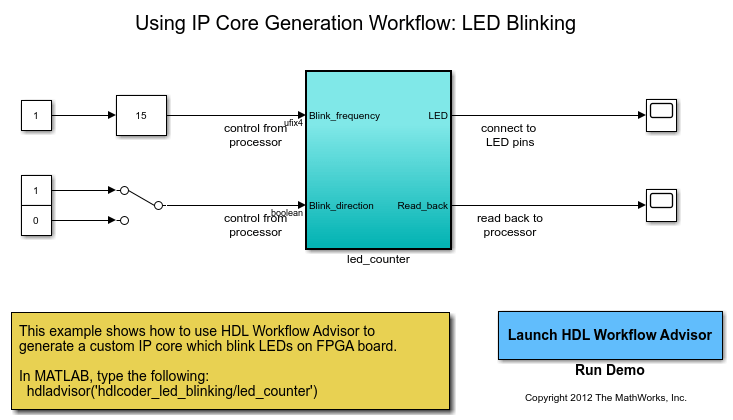

Выберите DUT в модели Simulink и откройте HDL Workflow Advisor. Например, откройте модель hdlcoder_led_blinking.

open_system('hdlcoder_led_blinking')

Установите путь к установленному инструменту синтеза для целевого устройства при помощи hdlsetuptoolpath функция. Например, если Xilinx Vivado® инструмент синтеза, используйте команду:

hdlsetuptoolpath('ToolName','Xilinx Vivado','ToolPath',... 'C:\Xilinx\Vivado\2018.2\bin\vivado.bat');

Смотрите Поддержку Языка HDL и Поддерживаемые Сторонние программы и Оборудование для последней поддерживаемой версии инструмента синтеза.

Откройте HDL Workflow Advisor для Подсистемы DUT. Для LED мигающая модель, led_counter Подсистема является DUT. В Set Target> задача Set Target Device and Synthesis Tool:

Для Target workflow выберите IP Core Generation.

Для Target platform, в зависимости от инструмента синтеза и устройства, для которого вы предназначаетесь, выберите Generic Altera Platform или Generic Xilinx Platform. Нажмите Run This Task.

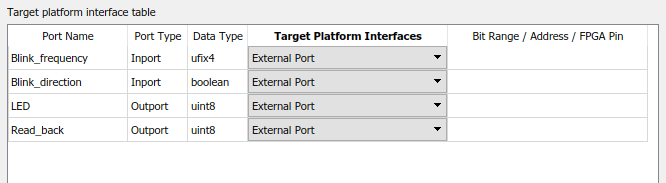

В Set Target> задача Set Target Interface, выберите Target Platform Interface для каждого порта, и затем нажмите Apply. Можно сопоставить каждый порт DUT с одним из этих интерфейсов: AXI4-Lite, AXI4, AXI4-Stream, AXI4-Stream Video, External Port, или FPGA Data Capture - JTAG. Для получения дополнительной информации об этих интерфейсах, смотрите Интерфейсы Целевой платформы.

Можно также сопоставить порты с несколькими интерфейсами целевой платформы. Чтобы узнать больше, смотрите, Генерируют Ядро IP HDL с Несколькими, AXI4-передают-потоком и Основные Интерфейсы AXI4.

Если вы не хотите сопоставлять порты DUT с ведомыми интерфейсами AXI4, можно сопоставить их с External Port интерфейсы.

Расширьте задачу Set Code Generation Options. Щелкните правой кнопкой по задаче Set Optimization Options и выберите Run to Selected Task.

В HDL Code Generation> задача Generate RTL Code and IP Core, можно задать:

Хотите ли вы соединить ядро IP DUT с несколькими Основными интерфейсами AXI. По умолчанию значением AXI4 Slave ID Width является 12, который позволяет вам соединить ядро IP HDL с одним интерфейсом AXI Master. Чтобы соединить ядро IP DUT с несколькими Основными интерфейсами AXI, можно хотеть увеличить AXI4 Slave ID Width. Когда вы запускаете эту задачу, эта установка сохранена на DUT как свойство AXI4SlaveIDWidth блока HDL.

Чтобы узнать больше, смотрите, Задают Несколько Основных Интерфейсов AXI в Исходных проектах, чтобы получить доступ к Ведомому Интерфейсу DUT AXI4.

Хотите ли вы сгенерировать ведомый интерфейс AXI4 по умолчанию. По умолчанию HDL Coder™ генерирует ведомые интерфейсы AXI4 для сигналов, таких как часы, сброс, готовый, метка времени, и так далее. Если вы не хотите генерировать какие-либо ведомые интерфейсы AXI4, снимите флажок Generate default AXI4 slave interface.

Примечание

Если вы сопоставили какой-либо из портов DUT к ведомым интерфейсам AXI4 в задаче Set Target Interface, генератор кода сопоставляет порты с ведомыми интерфейсами AXI4, снимается ли флажок Generate default AXI4 slave interface.

Нажмите Run This Task. Когда вы снимаете флажок и запускаете задачу, генератор кода сохраняет эту настройку на Подсистеме DUT как свойство GenerateDefaultAXI4Slave блока HDL.

После выполнения задачи HDL Coder генерирует файлы ядра IP в выходной папке, показанной поле IP core folder, включая документацию HTML. Чтобы просмотреть отчет ядра IP, щелкните по ссылке в окне сообщения.

Когда вы запускаете IP Core Generation рабочий процесс, можно также сгенерировать ядро IP HDL без любых ведомых интерфейсов AXI4 в исходном проекте.

Чтобы запустить этот рабочий процесс, откройте HDL Workflow Advisor, задайте Generic Xilinx Platform или Generic Altera Platform как целевая платформа и карта порты DUT только к Внешнему порту или интерфейс AXI4-Stream с отображением TLAST. Кроме того, когда вы генерируете ядро IP HDL, в задаче Generate RTL Code and IP Core, снимаете флажок Generate default AXI4 slave interface, и затем выбираете Run This Task.

Используйте эту возможность когда:

Вы не хотите настраивать параметры ядра IP при помощи ведомых интерфейсов AXI4.

Вы хотите создать пользовательский исходный проект без ведомых интерфейсов AXI4, таких как автономные платы FPGA.

Кроме того, предотвращение генерации ведомых интерфейсов AXI4 в таких случаях уменьшает использование аппаратного ресурса и сложность проекта.

Примечание

Внешний IO и внутренние интерфейсы IO соединяют ваше ядро IP HDL с другим существующим дюйм/с в вашем пользовательском исходном проекте. Чтобы задать эти интерфейсы, вы используете addInternalIOInterface и addExternalIOInterface методы hdlcoder.ReferenceDesign класс.

Чтобы интегрировать ядро IP HDL, можно создать пользовательский исходный проект без ведомых интерфейсов AXI4. В пользовательском исходном проекте можно только использовать Внешний IO, Внутренний интерфейс IO или AXI4-Stream с отображением TLAST. Для примеров см.:

Когда вы генерируете ядро IP HDL без ведомых интерфейсов AXI4, определенные ограничения применяются. Смотрите Ядро IP без Ведомых Интерфейсных Ограничений AXI4.

DUT должен быть атомарной системой.

То же ядро IP не может использовать и интерфейс AXI4 и интерфейс AXI4-Lite.

DUT не может содержать Системные блоки Генератора Xilinx или Разработчика DSP Intel Усовершенствованные блоки.

Если ваш выходной язык является VHDL®, и вашим инструментом синтеза является Xilinx ISE или Intel Куарт Прайм, DUT не может содержать модель - ссылку.

Порты ввода и вывода должны иметь немного ширины, меньше чем или равной 32 битам.

Порты ввода и вывода должны быть скаляром.

Порты должны иметь 32-битную ширину.

Порты должны быть скаляром.

У вас может быть максимум одного входного видеопорта и одного выходного видеопорта.

AXI4-потоковый Видеоинтерфейс не поддерживается в Coprocessing – blocking режим. Processor/FPGA synchronization должен быть установлен в Free running режим.

Можно только сопоставить порты с Внешними/Внутренними интерфейсами IO или интерфейсом AXI4-Stream с отображением TLAST. Другие интерфейсы, которые требуют ведомых интерфейсов AXI4, таких как Ведущее устройство AXI4, AXI4-поток и AXI4-потоковое Видео, не поддерживаются.

Необходимо использовать Free running режим для Processor/FPGA synchronization. Coprocessing – blocking режим не поддерживается.