Рассмотрите использование этих рекомендуемых настроек, когда вы создадите свою модель иерархически и сгенерируете HDL-код для вашего проекта. Каждая инструкция имеет уровень серьезности, который указывает на уровень требований податливости. Чтобы узнать больше, смотрите Уровни серьезности Руководств по моделированию HDL.

ID инструкции

1.2.4

Серьезность

Обязательный

Описание

Рекомендуется, чтобы вы постарались не непосредственно соединять блоки Константа с выходными портами Подсистемы. Инструменты синтеза могут оптимизировать и удалить константы и создать неподключенные порты.

Если вы используете типы данных с плавающей точкой с Native Floating Point режим включил и ввел постоянные значения арифметическому оператору, такие как блок Add, HDL Coder™ заменяет блок Add на блок Constant при генерации кода. Эта оптимизация может привести к блоку Constant, непосредственно соединенному с выходным портом. Поэтому рекомендуется, чтобы вы избежали таких построений моделирования. См. также Упрощают Постоянные Операции и Уменьшают Сложность Проекта в HDL Coder.

Например, откройте модель hdlcoder_constant_subsystem_boundary.slx. DUT содержит две подсистемы Constant_subsys1 и Constant_subsys2, выходные параметры которого являются входными параметрами к третьей Подсистеме. Constant_subsys1 содержит блоки Константа, непосредственно соединенные с выходными портами и Constant_subsys2 содержит блоки Константа, которые имеют один типы данных как входные параметры с блоком Add.

load_system('hdlcoder_constant_subsystem_boundary.slx') set_param('hdlcoder_constant_subsystem_boundary','SimulationCommand','Update') open_system('hdlcoder_constant_subsystem_boundary/DUT/Constant_subsys1')

open_system('hdlcoder_constant_subsystem_boundary/DUT/Constant_subsys2')

Как Constant_subsys2 использование один типы данных и модель имеет Native Floating Point режим включил, когда вы генерируете HDL-код для DUT, Constant_subsys2 становится кандидатом на оптимизацию, которая упрощает постоянные операции. Когда вы открываете сгенерированную модель, вы видите блок Constant, непосредственно соединенный с выходным портом.

open_system('gm_hdlcoder_constant_subsystem_boundary.slx') set_param('gm_hdlcoder_constant_subsystem_boundary','SimulationCommand','Update') open_system('gm_hdlcoder_constant_subsystem_boundary/DUT/Constant_subsys2')

ID инструкции

1.2.5

Серьезность

Рекомендуемый

Описание

Сгенерировать параметрированный HDL-код для блоков Усиления и Константа:

Подсистема, которая содержит блоки Усиления и Константа, должна быть подсистемой маскированной. Блоки Усиления и Константа используют эти значения параметров маски. Вы задаете параметры маски Подсистемы в диалоговом окне Mask Editor.

Подсистемой, которая содержит блоки Усиления и Константа, должна быть Атомарная подсистема. Чтобы сделать Подсистему Атомарной подсистемой, щелкните правой кнопкой по той Подсистеме и выберите Treat как атомарный модуль.

Включите Генерировать параметрированный HDL-код из установки подсистемы маскированной в диалоговом окне Configuration Parameters или установите MaskParameterAsGeneric к on в командной строке с помощью makehdl или hdlset_param.

Для примера откройте модель hdlcoder_masked_subsystems. Top Подсистема содержит две атомарных подсистемы маскированных MASKSUB и MASKSUB1 это подобно, но для значений параметров маскированных.

load_system('hdlcoder_masked_subsystems') set_param('hdlcoder_masked_subsystems', 'SimulationCommand', 'Update') open_system('hdlcoder_masked_subsystems/TOP')

Модель имеет MaskParameterAsGeneric установка включена. Эта установка соответствует Тому, чтобы генерировать параметрированный HDL-код от подсистемы маскированной, устанавливающей, который включен в командной строке.

hdlsaveparams('hdlcoder_masked_subsystems')

%% Set Model 'hdlcoder_masked_subsystems' HDL parameters

hdlset_param('hdlcoder_masked_subsystems', 'HDLSubsystem', 'hdlcoder_masked_subsystems/TOP');

hdlset_param('hdlcoder_masked_subsystems', 'MaskParameterAsGeneric', 'on');

Сгенерировать код VHDL для Top Подсистема, запустите эту команду:

makehdl('hdlcoder_masked_subsystems/TOP')

В сгенерированном коде вы видите, что HDL Coder™ генерирует один файл HDL MaskedSub различными параметрами маскированными, сопоставленными с типовыми портами.

-- -------------------------------------------------------------

--

-- File Name: hdlsrc\hdlcoder_masked_subsystems\TOP.vhd

-- Created: 2018-10-08 13:30:02

--

-- Generated by MATLAB 9.6 and HDL Coder 3.13

--

--

-- -------------------------------------------------------------

--

--

ARCHITECTURE rtl OF TOP IS

-- Component Declarations

COMPONENT MASKSUB

GENERIC( m : integer;

b : integer

);

PORT( x : IN std_logic_vector(7 DOWNTO 0); -- uint8

y : OUT std_logic_vector(16 DOWNTO 0) -- ufix17

);

END COMPONENT;

-- Component Configuration Statements

FOR ALL : MASKSUB

USE ENTITY work.MASKSUB(rtl);

-- Signals

SIGNAL MASKSUB_out1 : std_logic_vector(16 DOWNTO 0); -- ufix17

SIGNAL MASKSUB1_out1 : std_logic_vector(16 DOWNTO 0); -- ufix17

BEGIN

u_MASKSUB : MASKSUB

GENERIC MAP( m => 5,

b => 2

)

PORT MAP( x => In1, -- uint8

y => MASKSUB_out1 -- ufix17

);

u_MASKSUB1 : MASKSUB

GENERIC MAP( m => 6,

b => 4

)

PORT MAP( x => In1, -- uint8

y => MASKSUB1_out1 -- ufix17

);

Out1 <= MASKSUB_out1;

Out2 <= MASKSUB1_out1;

END rtl;

1.2.6

Обязательный

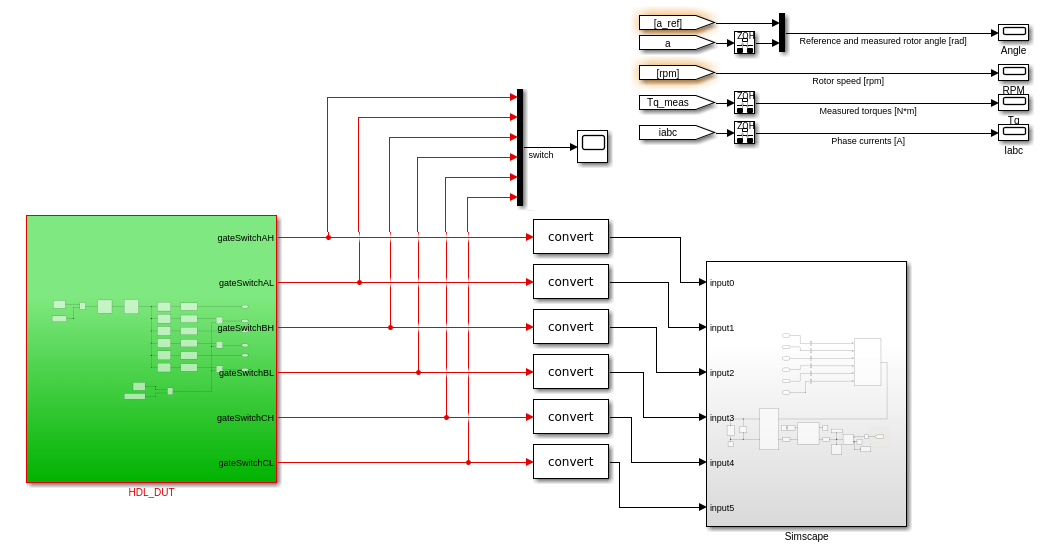

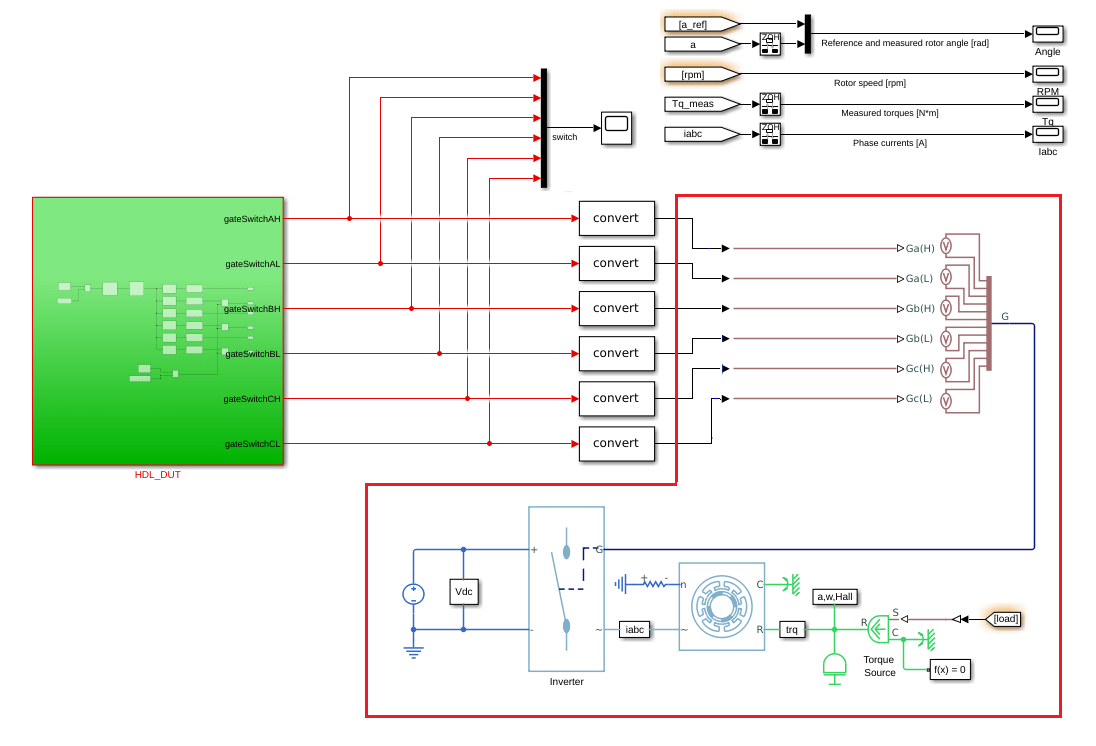

Чтобы избежать ошибок при генерации испытательного стенда HDL, линии физического сигнала, которые присутствуют на том же уровне как подсистема DUT, должны быть помещены в блоке Subsystem. Например, рассмотрите этот Simulink® модель, которая имеет линии физического сигнала вне подсистемы DUT, HDL_DUT.

Поместите линии физического сигнала и блоки, соединенные с ним, которые подсвечены в блоке Subsystem. Можно затем сгенерировать HDL-код и испытательный стенд для подсистемы DUT.