Для целевых платформ, которые поддерживают IP Core Generation рабочий процесс с Xilinx® Vivado®, можно использовать кэширование IP. Кэширование IP уменьшает время синтеза исходных проектов, которые имеют много модулей IP или которые имеют модули IP со значительным временем выполнения синтеза. Когда вы включаете кэширование IP, проект Vivado использует рабочий процесс из контекста (OOC). Этот рабочий процесс синтезирует IP в исходном проекте из контекста из проекта верхнего уровня. Рабочий процесс OOC ускоряет запуски проекта, потому что инструмент синтеза снова использует кэш IP и не должен повторно синтезировать IP, когда вы запускаете рабочий процесс.

Если вы не включаете кэширование IP, по умолчанию, проект Vivado использует глобальный поток синтеза. Этот поток синтезирует модули IP в исходном проекте наряду с проектом верхнего уровня. В последующих запусках проекта этот рабочий процесс повторно синтезирует модули IP в исходном проекте.

Target workflow:

IP Core Generation

Simulink Real-Time FPGA I/O для плат Speedgoat то использование Xilinx Vivado

Synthesis tool: Xilinx Vivado

Кэш IP является папкой, которая состоит из подпапок, соответствующих модулям IP в исходном проекте. Каждая подпапка организована индексом хеша, который соответствует имени файла. Для каждого модуля IP подпапка состоит из файлов Экземпляра ядра Xilinx (XCI), Контрольная точка Проекта (DCP) файлы и файлы журнала синтеза. DCP является контейнерным файлом, который содержит синтезируемые списки соединений, файлы заглушки HDL черного квадрата и выходные ограничения часов.

Чтобы снова использовать кэш IP, когда вы запускаете рабочий процесс, синтез IP должен совпадать с индексом хеша в кэше IP. Соответствие индекса хеша соответствует хиту в кэше IP. Чтобы поразить кэш IP в последующих запусках, используйте то же самое:

Часть, язык и настройки целевой платформы

Версия исходного проекта

Целевая частота

hdl_prj папка, когда вы создали кэш IP

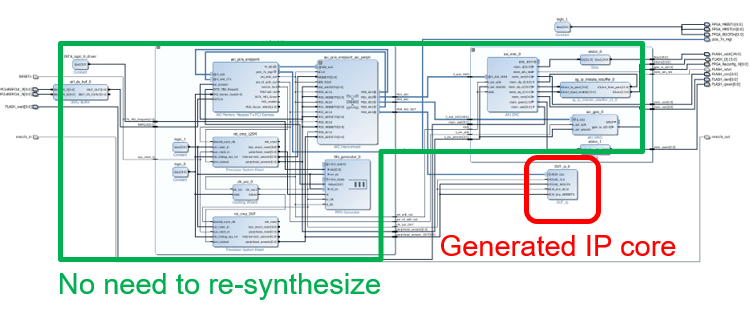

Когда вы включаете кэширование IP, проект Xilinx Vivado использует рабочий процесс из контекста (OOC). Процесс проектирования OOC является восходящим рабочим процессом что:

Синтезирует модули IP в исходном проекте отдельно из проекта верхнего уровня. Синтез выход является Контрольной точкой Проекта (DCP) файл.

Синтезирует ваш проект верхнего уровня при обработке IP в исходном проекте как черный квадрат при помощи файлов заглушки HDL, которым предоставляют DCP.

Реализует ваш проект на целевом устройстве путем соединения списков соединений от файлов контрольной точки проекта IP со списком соединений верхнего уровня.

Для больших исходных проектов поток OOC улучшает время выполнения синтеза, потому что вы не должны повторно синтезировать IP, когда вы изменяете свой проект и запускаете рабочий процесс. Чтобы узнать больше о рабочем процессе OOC и опциях синтеза IP, обратитесь к документации Xilinx.

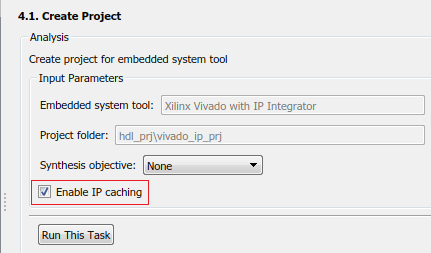

Прежде чем вы включите кэширование IP, зададите IP Core Generation как целевой рабочий процесс, и затем задают настройки целевой платформы. Включить кэширование IP:

От HDL Workflow Advisor, в задаче Create Project, устанавливают флажок Enable IP caching.

Из командной строки используйте EnableIPCaching свойство hdlcoder.WorkflowConfig класс. Чтобы использовать это свойство, создайте объект hdlcoder.WorkflowConfig класс или экспорт настройки HDL Workflow Advisor к скрипту.

hWC = hdlcoder.WorkflowConfig('SynthesisTool','Xilinx Vivado','TargetWorkflow','IP Core Generation'); % ... % ... hWC.EnableIPCaching = true;

Используйте IP, кэширующийся для больших исходных проектов, которые имеют значительное время синтеза. Например, исходный проект HDL Coder™ Default video system (requires HDMI FMC module) потенциальный кандидат на кэширование IP.

Примечание

Speedgoat IO333-325K плата, которую вы используете с Simulink Real-Time FPGA I/O рабочий процесс идет с кэшем IP. Первый раз, когда вы запускаете рабочий процесс, генератор кода, снова использует этот кэш IP, который улучшает время синтеза исходного проекта.

Чтобы включить кэширование IP, в HDL Workflow Advisor, задают IP Core Generation как целевой рабочий процесс, и затем задают настройки целевой платформы. Прежде чем вы запустите рабочий процесс впервые:

В задаче Create Project установите флажок Enable IP caching.

Когда вы запускаете эту задачу, рабочий процесс создает пустую папку кэша IP. Вы видите ipcache папка в hdl_prj/vivado_ip_prj path.

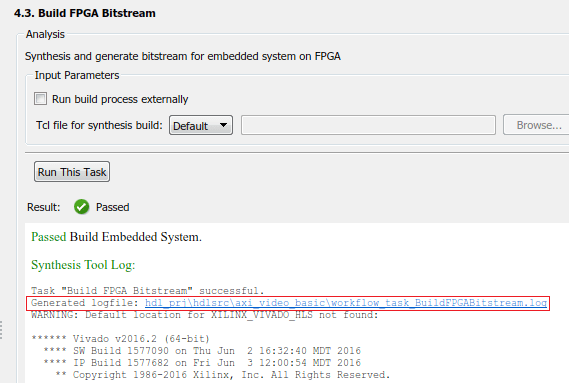

Запустите задачу Build FPGA Bitstream.

Эта задача заполняет папку кэша IP с журналами синтеза и файлами контрольной точки проекта, сгенерированными для ядра IP HDL и других блоков IP в исходном проекте. Когда эта задача запустилась успешно, вы видите сгенерированные файлы в ipcache папка.

Когда вы запускаете IP Core Generation рабочий процесс во второй раз, в задаче Build FPGA Bitstream, вы видите улучшение во время выполнения задачи. Убедитесь, что вы используете те же настройки IP и hdl_prj папка как в первый раз, когда вы запустили рабочий процесс. Когда эта задача запустилась успешно, чтобы видеть, снова использовал ли ваш рабочий процесс кэш IP, откройте workflow_task_buildFPGABitstream.log файл.

Этот фрагмент кода показывает, что проект Vivado запускает максимальное количество заданий, чтобы синтезировать проект и снова использовать модули IP в папке кэша IP. Вы видите что cacheID из IP модули совпадают с именами файлов подпапок в ipcache папка.

... # reset_run impl_1 # reset_run synth_1 # launch_runs -jobs 4 synth_1 ... ... ... INFO: [IP_Flow 19-4760] Using cached IP synthesis design for IP system_top_RGBtoYCbCr_0_0, cacheID = 3575924730488800 INFO: [IP_Flow 19-4760] Using cached IP synthesis design for IP system_top_YCbCrtoRGB_0_0, cacheID = e71459f41e26e141 INFO: [IP_Flow 19-4760] Using cached IP synthesis design for IP system_top_xbar_0, cacheID = d0f0971cb77bcaed INFO: [IP_Flow 19-4760] Using cached IP synthesis design for IP system_top_axis2hdmi_0_0, cacheID = 7601a322f9fd0ec4 ...

Если вы используете свой собственный исходный проект, кэширование IP может ускорить синтез исходного проекта, когда вы запускаете рабочий процесс впервые. Чтобы снова использовать кэш IP, создайте zip-файл кэша IP, и затем убедитесь, что файл определения исходного проекта указывает на этот zip-файл.

Создать zip-файл кэша IP:

Откройте HDL Workflow Advisor для любого Simulink® модель, которая имеет подсистему DUT, и затем запускает рабочий процесс IP Core Generation к задаче Generate RTL Code and IP Core.

В задаче Create Project установите флажок Enable IP caching, и затем нажмите Run This Task. Эта задача создает пустую папку кэша IP.

Запустите рабочий процесс к задаче Build FPGA Bitstream. Эта задача заполняет кэш IP с ядром IP HDL и модулями IP исходного проекта.

В папке кэша IP удалите файлы ядра IP, сгенерированные для DUT. Извлеките остающиеся файлы из этой папки в zip-файл, назовите ее ipcache.zip, и затем сохраните файл в папке исходного проекта.

Снова использовать кэш IP, в файле определения исходного проекта plugin_rd.m, используйте IPCacheZipFile свойство hdlcoder.ReferenceDesign класс. При помощи того свойства вы добавляете ipcache.zip файл к проекту Xilinx Vivado.

function hRD = plugin_rd() % Reference design definition hRD = hdlcoder.ReferenceDesign('SynthesisTool', 'Xilinx Vivado'); % ... % ... hRD.IPCacheZipFile = 'ipcache.zip';

hdlcoder.Board | hdlcoder.ReferenceDesign