К быстрому прототипированию нейронные сети для глубокого обучения на FPGAs из MATLAB®, используйте управляемый процессор глубокого обучения MATLAB. Процессор интегрирует типовой процессор глубокого обучения с MATLAB HDL Verifier™ как Ведущий IP AXI. Для получения дополнительной информации о:

Типовой процессор IP глубокого обучения, см. Приложения Процессора Глубокого обучения.

MATLAB как Ведущий IP AXI, смотрите Настроенный для MATLAB Ведущее устройство AXI (HDL Verifier).

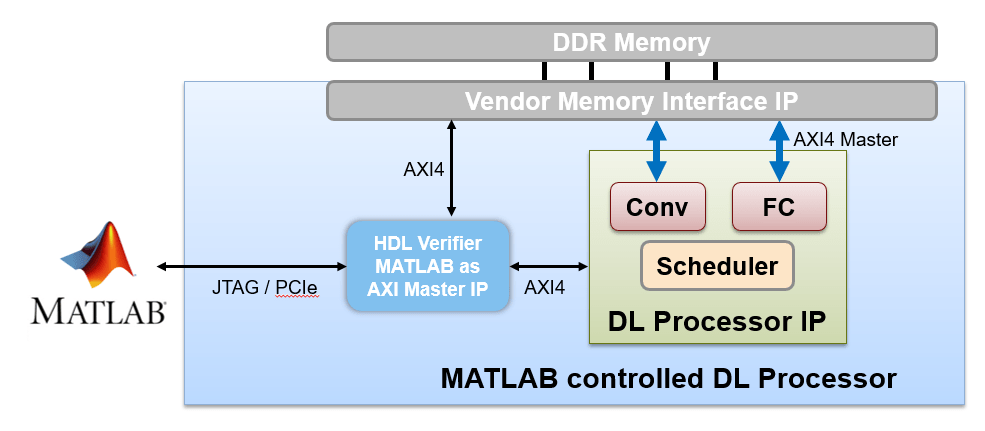

Можно использовать этот процессор, чтобы запустить нейронные сети с различными входными параметрами, весами и смещениями на той же платформе FPGA, потому что ядро процессора IP глубокого обучения может обработать тензоры и формы любых размеров. Прежде чем вы будете использовать MATLAB в качестве Ведущего устройства AXI, убедитесь, что вы установили пакеты поддержки HDL Verifier для плат FPGA. Этот рисунок показывает, что MATLAB управлял архитектурой процессора глубокого обучения.

Чтобы интегрировать типовой процессор IP глубокого обучения с MATLAB как Ведущее устройство AXI, используйте интерфейс AXI4 Slave ядра процессора IP глубокого обучения. При помощи JTAG или интерфейса экспресса PCI, IP отвечает на чтение или команды записи из MATLAB. Поэтому можно использовать управляемый процессор глубокого обучения MATLAB, чтобы развернуть глубокую нейронную сеть в платы FPGA из MATLAB, выполнить операции, заданные сетевой архитектурой, и затем возвратить предсказанные результаты к MATLAB. Следующий пример иллюстрирует, как развернуть предварительно обученную серийную сеть, AlexNet, к Intel® Arria® 10 комплектов разработчика SoC.