Децимирующий фильтр конечной импульсной характеристики (FIR) — оптимизированный для генерации HDL-кода

Поддержка HDL DSP System Toolbox / фильтрация

Блок FIR Decimation HDL Optimized реализует многофазный КИХ-децимирующий фильтр, который оптимизирован для генерации HDL-кода. Блок обеспечивает благоприятный для оборудования интерфейс с управляющими сигналами ввода и вывода. Обеспечить точную циклом симуляцию сгенерированного HDL-кода, модели блока архитектурная задержка включая регистры трубопровода и разделение ресурсов.

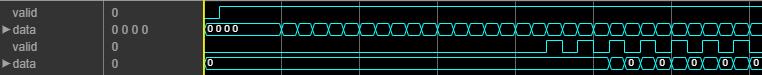

Блок принимает скалярный или векторный вход. Когда вы используете векторный вход, фактором децимации должно быть целочисленное кратное размер вектора. Блок использует односкоростную реализацию. Выход является скаляром, и допустимый сигнал указывает, какие выборки допустимы после децимации. Форма волны показывает входной вектор четырех выборок и фактор децимации восемь. Выходная выборка допустима каждый второй цикл.

Блок обеспечивает две структуры фильтра. Систолическая архитектура прямой формы обеспечивает полностью параллельную реализацию, которая делает эффективное использование Intel® и Xilinx® Блоки DSP. Транспонированная архитектура прямой формы является полностью параллельной реализацией, которая подходит для приложений ASIC и FPGA. Для реализации фильтра, которая совпадает со множителями, регистры трубопровода и предварительные сумматоры к настройке DSP вашего поставщика FPGA, задают ваше целевое устройство, когда вы генерируете HDL-код.

Блок реализует один фильтр для каждой выборки во входном векторе. Блок затем совместно использует этот фильтр между многофазными подфильтрами путем перемежения коэффициентов подфильтра вовремя.

Для КИХ-децимирующего фильтра с входным размером, больше фактор децимации или последовательная реализация HDL (скаляр ввел только), используйте блок FIR Decimation вместо этого блока.

Сбросьте поведение

По умолчанию блок FIR Decimation HDL Optimized соединяет сгенерированный глобальный сброс HDL только с регистрами пути к управлению. Два параметра сброса, Enable reset input port и Use HDL global reset, соединяют сигнал сброса с регистрами информационного канала. Из-за дополнительной маршрутизации и загрузки на сигнал сброса, сбрасывая регистры информационного канала может уменьшать эффективность синтеза.

Параметр Enable reset input port включает порт reset на блоке. Сигнал сброса реализует локальный синхронный сброс регистров информационного канала. Для оптимального использования ресурсов FPGA эта опция не соединяет сигнал сброса с регистрами, предназначенными с блоками DSP FPGA.

Параметр Use HDL global reset соединяет сгенерированный глобальный сигнал сброса HDL с регистрами информационного канала. Этот параметр не изменяет внешний вид блока или изменяет поведение симуляции в Simulink. Сгенерированный глобальный сброс HDL может быть синхронным или асинхронным в зависимости от HDL Code Generation> Global Settings> параметр Reset type в модели Configuration Parameters. В зависимости от вашего устройства, с помощью глобального сброса может переместить регистры из блоков DSP и увеличить использование ресурса.

Когда вы выбираете Enable reset input port и параметры Use HDL global reset вместе, глобальная переменная и локальные сигналы сброса очищают регистры информационного канала и управление.

Сбросьте факторы для сгенерированных испытательных стендов

FPGA в инициализации цикла обеспечивает глобальный сброс, но автоматически не обеспечивает локальный сброс. Параметрами сброса по умолчанию регистры информационного канала, которые не сбрасываются, могут привести к FPGA в цикле (FIL) несоответствия, если вы запускаете модель FIL несколько раз, не сбрасывая плату. Выберите Use HDL global reset, чтобы сбросить регистры информационного канала автоматически, или выбрать Enable reset input port и утверждать локальный сброс в вашей модели, таким образом, сигнал сброса становится частью испытательного стенда FIL Simulink.

Сгенерированный испытательный стенд HDL обеспечивает глобальный сброс, но автоматически не обеспечивает локальный сброс. Параметрами сброса по умолчанию и Параметрами конфигурации сброса регистра по умолчанию, сгенерированный HDL-код включает начальное значение симуляции для регистров информационного канала. Однако, если вы обеспокоены X- распространение в вашем проекте, можно установить HDL Code Generation> Global Settings> Coding style> параметр No-reset register initialization в Параметрах конфигурации к Do not initialize. В этом случае, с блоком по умолчанию сбрасывает параметры, регистры информационного канала, которые не сбрасываются, могут вызвать X- распространение на информационном канале в начале симуляции HDL. Выберите Use HDL global reset, чтобы сбросить регистры информационного канала автоматически, или выбрать Enable reset input port и утверждать локальный сброс в вашей модели, таким образом, сигнал сброса становится частью сгенерированного испытательного стенда HDL.