Вычисления с фиксированной точкой относятся к тому, как управляются двоичные слова без знака или со знаком. Простота функций вычислений с фиксированной точкой, таких как сложение и вычитание допускает экономически эффективные аппаратные реализации.

Разделы, которые следуют, описывают правила что Simulink® программное обеспечение следует, когда арифметические операции выполняются на входных параметрах и параметрах. Эти правила организованы в четыре группы на основе включенных операций: сложение и вычитание, умножение, деление и сдвиги. Для каждой из этих четырех групп правилам для выполнения заданной операции дарят пример, использующий правила.

Базовая архитектура многих процессоров содержит несколько вычислительных модулей включая арифметико-логические устройства (ALUs), умножьте и накопите модули (MACS) и переключатели. Эти вычислительные модули обрабатывают двоичные данные непосредственно и оказывают поддержку для арифметических расчетов различной точности. ALU выполняет стандартный набор арифметических и логических операций, а также деления. MAC выполняет, умножают, умножаются/добавляют и умножаются/вычитают операции. Переключатель выполняет логические и арифметические сдвиги, нормализацию, денормализацию и другие операции.

Сложение является наиболее распространенной арифметической операцией, которую выполняет процессор. Когда два n-bit числа добавляются вместе, всегда возможно привести к результату с n + 1 ненулевая цифра из-за переноса от крайней левой цифры. Для сложения в дополнительном коде two двух чисел существует три случая, чтобы рассмотреть:

Если оба числа положительны, и результат их сложения имеет знаковый бит 1, то переполнитесь, произошел; в противном случае результат правилен.

Если оба числа отрицательны, и знак результата 0, то переполнитесь, произошел; в противном случае результат правилен.

Если числа имеют различающийся знак, переполнение не может произойти, и результат всегда правилен.

Рассмотрите суммирование двух чисел. Идеально, реальные значения выполняют уравнение

где Vb и Vc являются входными значениями, и Va является выходным значением. Чтобы видеть, как суммирование на самом деле реализовано, три идеальных значения должны быть заменены генералом [Наклонное Смещение] схема кодирования, описанная в Масштабировании:

Уравнение, кроме того, дает решение получившегося уравнения для сохраненного целого числа, Qa. Используя краткое обозначение, то уравнение становится

где Fsb и Fsc являются настроенными дробными наклонами, и Bnet является сетевым смещением. Оффлайновые преобразования и онлайновые преобразования и операции обсуждены ниже.

Оффлайновые Преобразования. Fsb, Fsc и Bnet вычисляются оффлайн с помощью раунда-к-самому-близкому и насыщения. Кроме того, Bnet хранится с помощью типа выходных данных.

Онлайновые Преобразования и Операции. Остающиеся операции выполняются онлайн процессором фиксированной точки и зависят от наклонов и смещений для типов входных и выходных данных. Худший (самый неэффективный) случай происходит, когда наклонам и смещениям не соответствуют. Худшие замены регистра и операции даны этими шагами:

Начальное значение для Qa дано сетевым смещением, Bnet:

Первое входное целочисленное значение, Qb, умножается на настроенный наклон, Fsb:

Предыдущий продукт преобразован в модифицированный тип выходных данных, где наклон один, и смещение является нулем:

Это преобразование включает любую необходимую битную перемену, округление или обработку переполнения.

Операция суммирования выполняется:

Это суммирование включает любую необходимую обработку переполнения.

Шаги 2 - 4 повторяются для каждого номера, который будет суммирован.

Важно отметить, что битная перемена, округление и обработка переполнения применяются к промежуточным шагам (3 и 4) а не к полной сумме.

Для получения дополнительной информации смотрите Процесс Суммирования.

Если масштабирование сигналов ввода и вывода является соответствующим, количество операций суммирования сокращено от худшего (самого неэффективного) случая. Например, когда вход имеет тот же дробный наклон как выход, шаг 2 уменьшает до умножения одним и может быть устранен. Тривиальные шаги в процессе суммирования устраняются и для симуляции и для генерации кода. Исключительное использование единственного двоичной точкой масштабирования и для входных сигналов и для выходных сигналов является распространенным способом устранить наклоны, которым не соответствуют, и смещения и результаты в самых эффективных симуляциях и сгенерированном коде.

Умножение n-bit двоичного числа с двоичным числом Мбит приводит к продукту, который является до m + n биты в длине и для подписанных и для слов без знака. Большинство процессоров выполняет n-bit n-bit умножением и приводит к 2n-bit результату (двойные биты) принимающий, что нет никакого условия переполнения.

Рассмотрите умножение двух чисел. Идеально, реальные значения выполняют уравнение

где Vb и Vc являются входными значениями, и Va является выходным значением. Чтобы видеть, как умножение на самом деле реализовано, три идеальных значения должны быть заменены генералом [Наклонное Смещение] схема кодирования, описанная в Масштабировании:

Решение получившегося уравнения для выхода сохранило целое число, Qa, приведен ниже:

Умножение с Ненулевыми Смещениями и Несовпадающими Дробными Наклонами. Реализация худшего случая вышеупомянутого уравнения происходит, когда наклонам и смещениям сигналов ввода и вывода не соответствуют. В таких случаях несколько низкоуровневых целочисленных операций требуются, чтобы выполнять высокоуровневое умножение (или деление). Выбор реализации, сделанный об этих низкоуровневых расчетах, может влиять на вычислительный КПД, погрешности округления и переполнение.

В блоках Simulink, фактическом умножении или операции деления всегда выполняется на переменных фиксированной точки, которые имеют нулевые смещения. Если вход имеет ненулевое смещение, он преобразован в представление, которое имеет единственное двоичной точкой масштабирование перед операцией. Если результат состоит в том, чтобы иметь ненулевое смещение, операция сначала выполняется с временными переменными, которые имеют единственное двоичной точкой масштабирование. Результат затем преобразован в тип данных и масштабирование окончательного результата.

Если и входные параметры и выход имеют ненулевые смещения, то операция сломана можно следующим образом:

где

Эти уравнения показывают, что временные переменные имеют единственное двоичной точкой масштабирование. Однако уравнения не указывают на размеры слова со знаком или значения фиксированной экспоненты этих переменных. Программное обеспечение Simulink присваивает эти свойства временным переменным на основе следующих целей:

Представляйте исходное значение без переполнения.

Тип данных и масштабирование исходного значения задают максимальное и минимальное реальное значение:

Тип данных и масштабирование временной ценности должны смочь представлять эту область значений без переполнения. Потеря точности возможна, но переполнение никогда не позволяется.

Используйте тип данных, который приводит к эффективным операциям.

Эта цель относительно цели, которую вы будете использовать для производственного развертывания своего проекта. Например, предположите, что вы реализуете проект на 16-битном процессоре фиксированной точки, который обеспечивает 32-битный long, 16-битный int, и 8-битный short или char. Для такой цели, сохраняя КПД означает, что не больше, чем 32 бита используются, и меньшие размеры 8 или 16 битов используются, если они достаточны, чтобы обеспечить точность.

Обеспечьте точность.

Идеально, каждое возможное значение, заданное исходным типом данных и масштабированием, представлено отлично временной переменной. Однако это может потребовать большего количества битов, чем эффективно. Биты отбрасываются, приводя к потере точности, до степени, требуемой сохранить КПД.

Например, рассмотрите следующее, приняв цель 16-разрядного микропроцессора:

где QOriginal является 8-битным, типом данных без знака. Для этого типа данных,

так

Минимальное возможное значение отрицательно, таким образом, временная переменная должна быть типом данных целого числа со знаком. Исходная переменная имеет наклон 1, но смещение описывается большей точностью с двумя цифрами после двоичной точки. Чтобы получить полную точность, фиксированная экспонента временной переменной должна быть-2 или меньше. Программное обеспечение Simulink выбирает наименее возможную точность, которая является обычно самой эффективной, если проблемы переполнения не возникают. Для масштабирования 2-2, выбор, подписанный 16-битный или подписанный 32-битный, избегает переполнения. Для КПД программное обеспечение Simulink выбирает меньший выбор 16 битов. Если исходная переменная является входом, то уравнения, чтобы преобразовать во временную переменную

Умножение с Нулевыми смещениями и Несовпадающими Дробными Наклонами. Когда смещения являются нулем, и дробным наклонам не соответствуют, реализация уменьшает до

Количество

вычисляется оффлайн с помощью раунда-к-самому-близкому и насыщения. FNet хранится с помощью типа данных с фиксированной точкой формы

где ENet и QNet выбраны автоматически, чтобы лучше всего представлять FNet.

Онлайновые преобразования и операции

Целочисленные значения Qb и Qc умножаются:

Чтобы обеспечить полную точность продукта, двоичная точка QRawProduct дана суммой двоичных точек Qb и Qc.

Предыдущий продукт преобразован в тип выходных данных:

Это преобразование включает любую необходимую битную перемену, округление или обработку переполнения. Преобразования сигнала обсуждают преобразования.

Умножение

выполняется.

Предыдущий продукт преобразован в тип выходных данных:

Это преобразование включает любую необходимую битную перемену, округление или обработку переполнения. Преобразования сигнала обсуждают преобразования.

Шаги 1 - 4 повторяются для каждого дополнительного номера, который будет умножен.

Умножение с Нулевыми смещениями и Соответствием с Дробными Наклонами. Когда смещения являются нулем и дробным соответствием наклонов, реализация уменьшает до

Никакие оффлайновые преобразования не выполняются.

Онлайновые преобразования и операции

Целочисленные значения Qb и Qc умножаются:

Чтобы обеспечить полную точность продукта, двоичная точка QRawProduct дана суммой двоичных точек Qb и Qc.

Предыдущий продукт преобразован в тип выходных данных:

Это преобразование включает любую необходимую битную перемену, округление или обработку переполнения. Преобразования сигнала обсуждают преобразования.

Шаги 1 и 2 повторяются для каждого дополнительного номера, который будет умножен.

Для получения дополнительной информации смотрите Процесс Умножения.

В этом разделе рассматриваются деление количеств с нулевым смещением.

Примечание

Когда любой вход к вычислению деления имеет ненулевое смещение, операции, выполняемые точно, совпадают с теми для умножения, описанного в Умножении с Ненулевыми Смещениями и Несовпадающими Дробными Наклонами.

Рассмотрите деление двух чисел. Идеально, реальные значения выполняют уравнение

где Vb и Vc являются входными значениями, и Va является выходным значением. Чтобы видеть, как деление на самом деле реализовано, три идеальных значения должны быть заменены генералом [Наклонное Смещение] схема кодирования, описанная в Масштабировании:

Для случая, где наклонные поправочные коэффициенты один и смещения, нуль для всех сигналов, решение получившегося уравнения для выхода сохранило целое число, обеспечение качества, дан следующим уравнением:

Это уравнение включает целочисленное деление и некоторые сдвиги разряда. Если Ea > Eb –Ec, то любые сдвиги разряда направо и реализация, прост. Однако, если Ea < Eb –Ec, то сдвиги разряда налево и реализация, может быть более сложным. Важный вопрос состоит в том, что выход имеет больше точности, чем целочисленное деление обеспечивает. Чтобы получить полную точность, дробное деление необходимо. Язык программирования C обеспечивает доступ к целочисленному делению только для типов данных с фиксированной точкой. В зависимости от размера числителя можно получить некоторые дробные биты путем выполнения сдвига до целочисленного деления. В худшем случае может быть необходимо обратиться к повторным вычитаниям в программном обеспечении.

В общем случае деление значений является операцией, которой нужно избежать во встраиваемых системах фиксированной точки. Деление, где выход имеет больше точности, чем целочисленное деление (т.е. Ea < Eb –Ec) должно использоваться с еще большим нежеланием.

Для получения дополнительной информации смотрите Процесс Деления.

Почти все микропроцессоры и цифровые сигнальные процессоры поддерживают четко определенный сдвиг разряда (или просто переключают), операции для целых чисел. Например, рассмотрите 8-битное беззнаковое целое 00110101. Результаты 2-битного сдвига налево и 2-битного сдвига направо показывают в следующей таблице.

| Операция сдвига | Двоичное значение | Десятичное значение |

|---|---|---|

Никакой сдвиг (исходный номер) | 00110101 | 53 |

Сдвиг оставлен на 2 бита | 11010100 | 212 |

Сдвиг прямо на 2 бита | 00001101 | 13 |

Можно выполнить сдвиг с помощью блока Simulink Shift Arithmetic. Используйте этот блок, чтобы выполнить немного сдвига, сдвиг двоичной точки или обоих

Особый случай сдвига битов направо требует фактора обработки крайнего левого бита, который может содержать информацию о знаке. Сдвиг направо может быть классифицирован или как право логического сдвига или как право арифметического сдвига. Для права логического сдвига 0 включен в старший значащий бит для каждого сдвига разряда. Для права арифметического сдвига старший значащий бит переработан для каждого сдвига разряда.

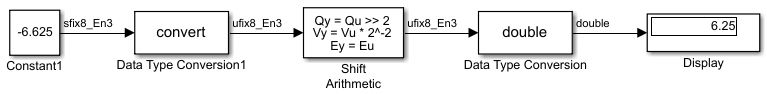

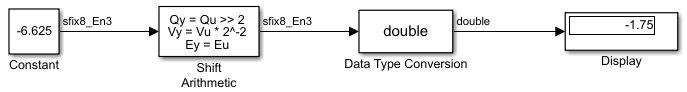

Блок Shift Arithmetic выполняет право арифметического сдвига и, поэтому, перерабатывает старший значащий бит для каждого права сдвига разряда. Например, учитывая фиксированную точку номер 11001.011 (-6.625), немного сдвига два места направо с двоичной точкой неперемещенные выражения номер 11110.010 (-1.75), как показано в модели ниже:

Чтобы выполнить логический сдвиг прямо на числе со знаком с помощью блока Shift Arithmetic, используйте блок Data Type Conversion, чтобы снять номер в качестве количества без знака эквивалентной длины и масштабирования. Эта модель показывает, что фиксированная точка число со знаком 11001.001 (-6.625) становится 00110.010 (6.25).