Поведенческая модель Триггера Шмитта

Simscape / Электрический / Интегральные схемы / Логика

Блок Schmitt Trigger реализует поведенческую модель Триггера Шмитта.

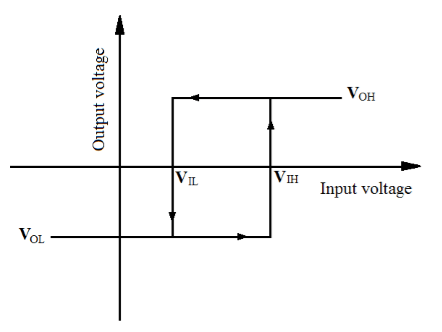

Выходным логическим уровнем блока является HIGH когда вход повышается выше High level input voltage (IH V) значение и не идет LOW пока вход не падает ниже Low level input voltage с более низким знаком (V IL) значение. Эта логика реализует гистерезисную характеристику между вводом и выводом.

В графическом, OH V и V ОЛ соответствуют High level output voltage и значениям Low level output voltage, соответственно.

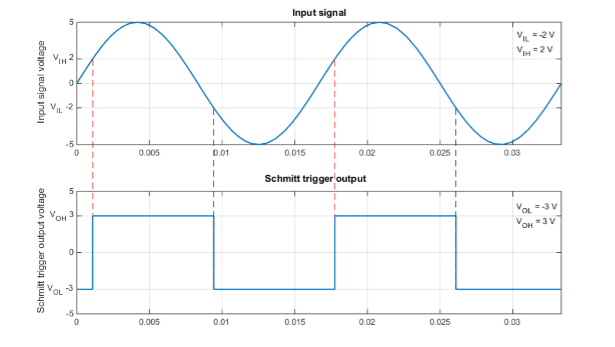

Следующий рисунок показывает демонстрационный выход блока параметрами IH V = 2 В, V IL =-2V, OH V = 3 В и V ОЛ =-3V.

Блок определяет логические уровни входных параметров логического элемента можно следующим образом:

Если напряжение затвора больше порогового напряжения, блок интерпретирует вход как логическую 1.

В противном случае блок интерпретирует вход как логический 0.

threshold voltage является значением напряжения в средней точке между значением параметров High level input voltage и значением параметров Low level input voltage.

Примечание

Чтобы улучшить скорость симуляции, блок не моделирует все внутренние отдельные устройства MOSFET, которые составляют логический элемент. Смотрите Предположения и Ограничения для деталей.

Блок моделирует логический элемент можно следующим образом:

Входные параметры логического элемента имеют бесконечное сопротивление и конечную или нулевую емкость.

Логический элемент вывел, предлагает выбор двух моделей: Linear и Quadratic. Для получения дополнительной информации смотрите Выбор Output Model for Logic Blocks. Используйте параметр Output current-voltage relationship, чтобы задать выходную модель.

Можно задать задержку распространения обеих выходных моделей. Для Linear выведите, блок устанавливает значение логического элемента выходной конденсатор, таким образом, что конденсаторная резистором постоянная времени равняется значению параметров Propagation delay. Для Quadratic выведите, спрос на вход логического элемента изолирован, чтобы аппроксимировать значение параметров Propagation delay.

Выходное напряжение блока зависит от выходной выбранной модели:

Для Linear модель, выход высоко является значением параметров High level output voltage, и выход низко является значением параметров Low level output voltage.

Для Quadratic модель, выходное напряжение для Высоких и Низких состояний является функцией текущего выхода, как объяснено в Квадратичном Выходе Модели и Параметрах. Для нулевой текущей загрузки выходом высоко является Vcc (значение параметров Supply voltage), и выход низко является нулевыми вольтами.

Блок не моделирует внутренние отдельные устройства MOSFET, которые составляют логический элемент (за исключением итоговой пары MOSFET, если вы выбираете Quadratic опция для параметра Output current-voltage relationship). Это ограничение имеет следующие последствия:

Блок точно не моделирует ответ логического элемента, чтобы ввести шум и входные параметры, которые являются вокруг логического порогового напряжения.

Блок точно не моделирует динамический ответ.

Для схем, которые включают путь к обратной связи вокруг набора логических элементов, вы можете должны быть установить ненулевую задержку распространения на одном или нескольких логических элементах.

Этот блок реализован с помощью уравнений события. Это означает, что необходимо обеспечить начальное состояние вывода, которое сопоставимо с входом блока в начальный момент времени. Например, если вы устанавливаете начальное состояние вывода HIGH, но начальное входное напряжение ниже Low level input voltage, затем начальный выход остается HIGH, состояние только исправление себя, когда входное напряжение повышается выше значения High level input voltage.

CMOS AND | CMOS Buffer | CMOS NAND | CMOS NOR | CMOS NOT | CMOS OR | CMOS XOR | S-R Latch