Декодируйте код LDPC с помощью разделенного на уровни распространения веры с суммой min или нормированным алгоритмом аппроксимации суммы min

Wireless HDL Toolbox / Выявление ошибок и Коррекция

Блок NR LPDC Decoder реализует декодер имеющей малую плотность проверки четности (LDPC) с благоприятными для оборудования управляющими сигналами. Блок принимает проколотые значения отношения логарифмической правдоподобности (LLR), поток управляющих сигналов, основного номера графика и подъема размеров. Блок выходные параметры декодировал биты, поток управляющих сигналов, снимая размеры и сигнал, который указывает, когда блок готов принять новые входные параметры.

Этот блок предоставляет возможность реализовывать разделенное на уровни распространение веры или с нормированным алгоритмом аппроксимации суммы min или с алгоритмом аппроксимации суммы min. Эта реализация соответствия та из функции nrLDPCDecode (5G Toolbox). Можно использовать этот блок для кодирования канала нисходящего канала, и восходящий канал совместно использовал каналы и канал разбивки на страницы согласно TS 38.212 [1] стандарта нового радио (NR) 5G.

Блок NR LDPC Decoder поддерживает скалярные и входные параметры вектор-столбца с 64 элементами. Блок поддерживает раннюю функцию завершения, чтобы помочь улучшать производительность декодирования и более быструю быстроту сходимости при высоких условиях шумового отношения сигнала (SNR). Блок позволяет декодировать нескольких скоростей кода, чтобы помочь достигнуть высокого КПД пропускной способности с высокой степенью гибкости скорости кода. Блок обеспечивает архитектуру, подходящую для аппаратного развертывания и генерации HDL-кода. Для получения дополнительной информации см. Алгоритмы.

data — Введите значения LLRВведите значения отношения логарифмической правдоподобности (LLR) в виде скаляра или вектор-столбца размера 64.

Тип данных этого входа должен быть типом данных с фиксированной точкой со знаком с размером слова от 4 до 16 битов. Для получения дополнительной информации о том, как задать векторные входные данные, смотрите Вход Вектора Определения.

Типы данных: int8 | int16 | fixed point

ctrl — Управляющие сигналы сопроводительный демонстрационный потокsamplecontrol шинаУправляющие сигналы, сопровождающие демонстрационный поток в виде samplecontrol шина. Шина включает startконец, и valid управляющие сигналы, которые указывают на контуры системы координат и валидность выборок.

start — Указывает на запуск входного кадра

end — Указывает на конец входного кадра

valid — Указывает, что данные по порту входа data допустимы

Для большего количества детали смотрите Демонстрационную Шину управления.

Типы данных: bus

bgn — Основной номер графикаОсновной номер графика в виде скаляра. Когда этим значением является 0, блок применяет bgn 1. Когда этим значением является 1, блок применяет bgn 2. Для получения дополнительной информации о bgn 1 и bgn 2, смотрите раздел 5.3.2 TS 38.212 [1].

Типы данных: Boolean

liftingSize — Введите подъем размераВведите подъем размера в виде скаляра.

Для недопустимого значения liftingSize блок отбрасывает текущую систему координат и ожидает новой системы координат. Для получения дополнительной информации о поддерживаемых поднимающихся значениях размера, смотрите раздел 5.3.2 TS 38.212 [1].

Типы данных: uint16

iter — Количество итерацийКоличество итераций в виде целого числа в диапазоне от 1 до 63.

Если вы задаете iter как значение, больше, чем 63, блок автоматически устанавливает значение iter к 8 и выполняет операцию декодирования.

Чтобы включить этот порт, установите параметр Source for number of iterations на Input port.

Типы данных: uint8

numRows — Количество строкКоличество строк в виде скаляра.

Когда вы устанавливаете значение bgn к 0 блок поддерживает количество строк в диапазоне от 4 до 46. Когда вы устанавливаете значение bgn к 1, блок поддерживает количество строк в диапазоне от 4 до 42.

Чтобы включить этот порт, выберите параметр Enable multiple code rates.

Типы данных: fixdt(0,6,0)

data — Декодируемые биты выходных данныхДекодируемые биты выходных данных, возвращенные как скаляр или вектор-столбец размера 64.

Блок выходные биты данных в аналогичном формате как значения входа LLR. Извлеките эти биты выходных данных в аналогичном формате для последующей обработки.

Типы данных: Boolean

ctrl — Управляющие сигналы сопроводительный демонстрационный потокsamplecontrol шинаУправляющие сигналы, сопровождающие демонстрационный поток, возвращенный как samplecontrol шина. Шина включает startконец, и valid управляющие сигналы, которые указывают на контуры системы координат и валидность выборок.

start — Указывает на запуск выходной системы координат

end — Указывает на конец выходной системы координат

valid — Указывает, что данные по порту выхода data допустимы

Для большего количества детали смотрите Демонстрационную Шину управления.

Типы данных: bus

liftingSize — Выведите подъем размераВыведите подъем размера, возвращенного как скаляр.

Типы данных: uint16

nextFrame — Блокируйте готовый индикаторБлокируйте готовый индикатор, возвращенный как булев скаляр.

Блок устанавливает этот сигнал на 1 TRUE) когда блок готов принять запуск следующей системы координат. Если блок получает сигнал входа ctrl.start, в то время как nextFrame является 0 ложь), блок отбрасывает происходящую систему координат и начинает обрабатывать новые данные.

Типы данных: Boolean

actIter — Фактическое количество итерацийФактическое количество итераций блок берет, чтобы декодировать выходной параметр, возвращенный как скаляр.

Чтобы включить этот порт, установите параметр Decoding termination criteria на Early.

Типы данных: uint8

parityCheck — Индикатор состояния проверки четностиИндикатор состояния проверки четности, возвращенный как булев скаляр. Порт указывает на состояние проверки четности после операции декодирования.

0 — Указывает, что проверка четности перестала работать

1 — Указывает, что проверка четности передала

Чтобы включить этот порт, выберите параметр Enable parity check output port.

Типы данных: Boolean

Algorithm — Тип алгоритмаMin-sum (значение по умолчанию) | Normalized min-sumВыберите тип алгоритма. Для получения дополнительной информации см. Алгоритм (5G Toolbox).

Scaling factor — Масштабный коэффициентЗадайте масштабный коэффициент.

Чтобы включить этот параметр, установите параметр Algorithm на Normalized min-sum.

Decoding termination criteria — Критерии завершенияMax (значение по умолчанию) | EarlyВыберите критерии завершения декодирования.

Max — Отключает декодирование, когда блок достигает количества итераций, заданных через параметр Number of iterations или через входной порт iter

Early — Отключает декодирование, когда всем проверкам четности соответствуют или когда блок достигает максимального количества итераций, заданных через параметр Maximum number of iterations или через входной порт iter

Source for number of iterations — Исходный выбор для количества итерацийProperty (значение по умолчанию) | Input portВыберите источник для определения количества итераций.

Можно определить номер итераций или при помощи входного порта или при помощи параметра.

Выберите Property включить или параметр Number of iterations или параметр Maximum number of iterations.

Выберите Input port включить порт iter.

Number of iterations — Количество итерацийЗадайте количество итераций.

Чтобы включить этот параметр, установите параметр Decoding termination criteria на Max и параметр Source for number of iterations к Property.

Maximum number of iterations — Максимальное количество итерацийЗадайте максимальное количество итераций.

Чтобы включить этот параметр, установите параметр Decoding termination criteria на Early и параметр Source for number of iterations к Property.

Enable multiple code rates — Несколько скоростей кодаoff (значение по умолчанию) | onВыберите этот параметр, чтобы позволить входному порту numRows поддержать несколько скоростей кода. Для получения дополнительной информации о нескольких скоростях кода, смотрите Несколько Скоростей кода.

Enable parity check output port — Состояние проверки четностиoff (значение по умолчанию) | onВыберите этот параметр, чтобы позволить выходному порту parityCheck просмотреть состояние проверки четности.

Векторные входные данные для блока должны быть заданы как вектор-столбец размера 64. Необходимо обеспечить входные параметры как целое число ceil(liftingSize/64) такты.

Общее количество тактов, которых блок требует, чтобы принять кадр значений LLR для декодирования, равно n x ceil(liftingSize/64), где n является количеством столбцов в матрице проверки четности. n зависит от основного номера графика, заданного входным портом bgn. Когда значением порта bgn является 0, блок устанавливает n на 66. Когда значением порта bgn является 1, блок устанавливает n на 50.

Эти разделы показывают, как блок принимает значения входа LLR на основе значений порта liftingSize и bgn.

Для входного значения liftingSize 2 и входное значение bgn 0, блок может принять 132 LLRs. В этом случае блок принимает первые два бита входа LLR за каждый такт и игнорирует остающиеся 62 элемента за тот такт. Общее количество тактов, которых блок требует, чтобы принять кадр значений LLR, равняется 66.

Элементы Ln представляют биты LLR, и эти X элементов представляют проигнорированные значения.

| Введите значения LLR | Количество тактов | |||||

|---|---|---|---|---|---|---|

| 1 такт | 2 такта | 3 такта | 4 такта | ... | 66 тактов | |

data[0] | L0 | L2 | L4 | L6 | ... | L130 |

data[1] | L1 | L3 | L5 | L7 | ... | L131 |

| ... | X | X | X | X | X | X |

data[63] | X | X | X | X | X | X |

Для входного значения liftingSize 104 и входное значение bgn 0, блок может принять 6,864 LLRs. В этом случае блок принимает 104 значения LLR за два такта: 64 LLRs за первый такт и 40 LLRs за второй такт. Блок игнорирует остающиеся 24 элемента за второй такт. Общее количество тактов, которых блок требует, чтобы получить значения входа LLR, равняется 132.

Элементы Ln представляют биты LLR, и эти X элементов представляют проигнорированные значения.

| Введите значения LLR | Количество тактов | |||||||

|---|---|---|---|---|---|---|---|---|

| 1 такт | 2 такта | 3 такта | 4 такта | ... | ... | 131 такт | 132 такта | |

data[0] | L0 | L64 | L104 | L168 | ... | ... | L6760 | L6824 |

data[1] | L1 | L65 | L105 | L169 | ... | ... | L6761 | L6825 |

| ... | ... | ... | ... | ... | ... | ... | ||

| ... | ... | L103 | ... | L207 | ... | ... | ... | L6863 |

| ... | ... | X | ... | X | ... | ... | ... | X |

data[63] | L63 | X | L167 | X | ... | ... | L6823 | X |

Коды NR LDPC могут поддержать гибкие скорости кода на основе расширения матрицы проверки четности (PCM), чтобы достигнуть высокой пропускной способности и удовлетворить низкие требования задержки. Блок поддерживает несколько скоростей кода путем варьирования количества строк матрицы проверки четности.

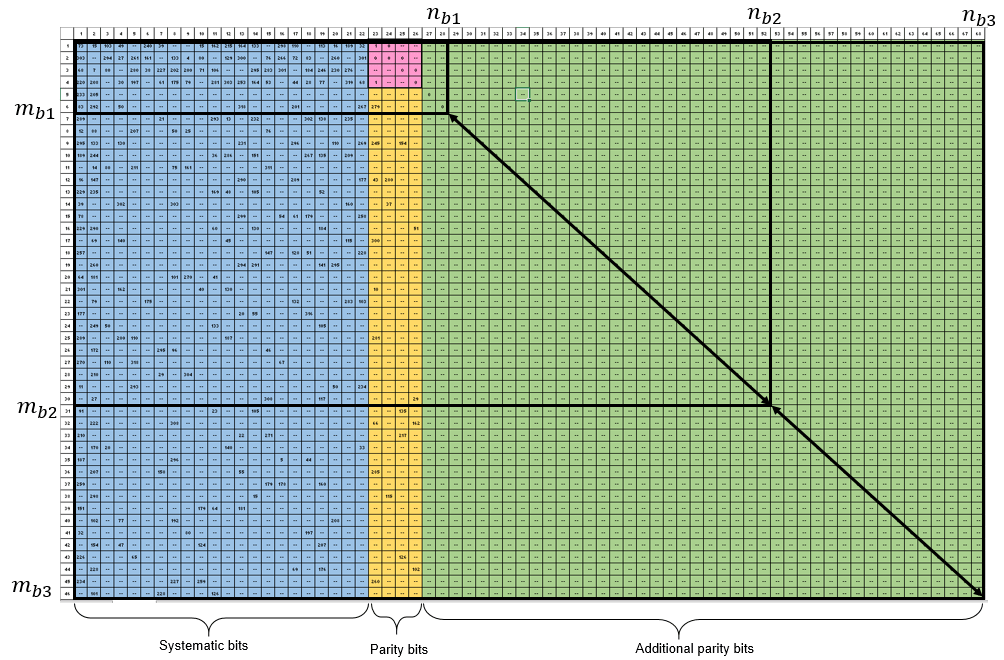

Для кодов LDPC основная матрица проверки четности (H b) является продуктом количества строк (m b) и количества столбцов (n b) матрицы. Выход (K) блока вычисляется как k b x Z, где Z является фактором расширения или подъемом размера, который может быть в диапазоне от 2 до 384, и kb равен 22 для значения bgn 0 и 10 для значения bgn 1 как задано в стандарте [1].

Входной размер (N) вычисляется как, n b x Z, где n b равен m b + k b.

Этот рисунок показывает матрицу проверки четности, отмеченную конкретным количеством строк и столбцов, которые можно использовать, чтобы вычислить скорости кода блока. Скорость кода R вычисляется как, k b / (k b – 2 + m b) для заданного значения bgn . В этом рисунке значения n b1, n b2 и n b3 указывают на количество столбцов для заданного значения bgn и значений m b1, m b2, и m b3 указывает на количество строк для заданного значения bgn.

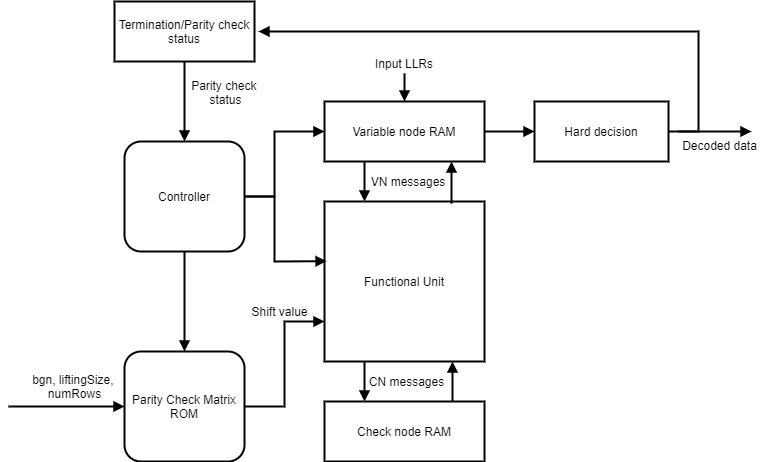

Этот рисунок показывает блок-схему архитектуры блока NR LDPC Decoder. Блок Controller управляет слоем и количеством итерации процесса декодирования. Блок RAM Узла переменной хранит сообщения узла переменной (VN), и блок RAM узла Проверки хранит сообщения узла проверки (CN). Блок Functional Unit вычисляет сообщения узла переменной (VN) и сообщения узла проверки (CN) на основе многоуровневого распространения веры и или нормированный алгоритм аппроксимации суммы min или алгоритм аппроксимации суммы min. Блок состояния Завершения/Проверки четности вычисляет проверки четности и обеспечивает состояние проверки четности после каждой итерации. Для получения дополнительной информации о декодировании алгоритмов, см. Алгоритм (5G Toolbox).

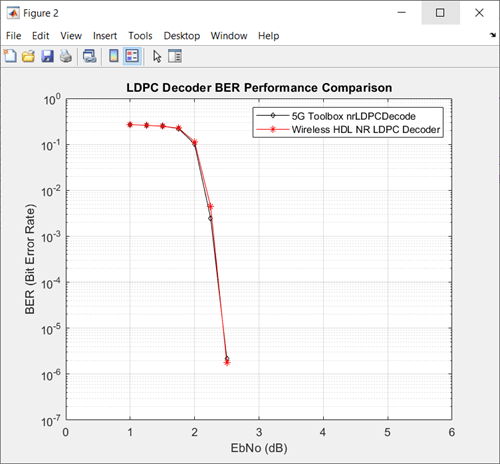

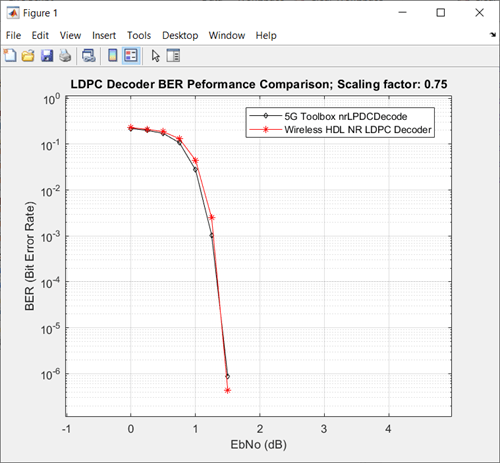

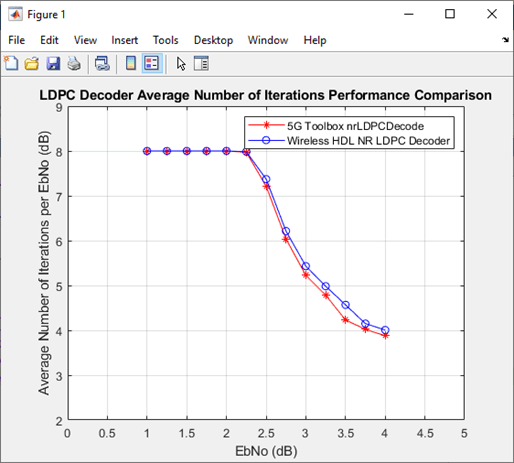

Реализация блока совпадает с эффективностью функции nrLDPCDecode (5G Toolbox).

Этот график показывает эффективность блока для 4-битного входа LLR, когда вы устанавливаете параметр Algorithm на Min-sum.

Этот график показывает эффективность блока для 4-битного входа LLR, когда вы устанавливаете параметр Algorithm на Normalized min-sum .

Этот график показывает среднее количество проделанных итераций, чтобы декодировать данные на EbNo для 4-битного входа LLR, когда вы устанавливаете параметр Algorithm на Min-sum и параметр Decoding termination criteria к Early.

Задержка блока варьируется на основе значений bgn, liftingSize, и входных портов numRows и количества итераций. Поскольку задержка варьируется, используйте выходной порт управляющего сигнала nextFrame, чтобы определить, когда блок готов к новому входному кадру.

Задержка блока равна r x (t + (m x 8) x ceil(liftingSize/64) + t + m x (7 – ceil(liftingSize/64))) + (n x liftingSize) + 18. В этом вычислении r является количеством итераций, n является количеством столбцов в матрице проверки четности, t является дважды общим количеством не –1 элемент в матрице проверки четности, m является количеством строк в матрице проверки четности, и d является задержками трубопровода. Когда вы выбираете параметр Enable multiple code rates, d равняется 26. В противном случае d равняется 18.

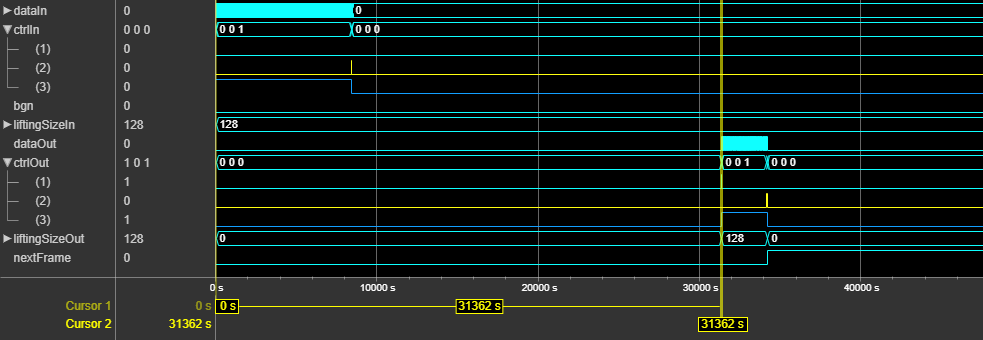

Этот рисунок показывает демонстрационный выход блока NR LDPC Decoder с задержкой. В этом случае bgn и значения входного порта liftingSize установлены в 0 и 128, соответственно, и параметр Number of iterations устанавливается на 8. Задержка блока является 31 362 тактами.

Для векторных входных параметров задержка блока равна r x (t + (m x 9)) + n x (ceil(liftingSize/64)) + d. В этом вычислении r является количеством итераций, n является количеством столбцов в матрице проверки четности, t является дважды общим количеством не-1 элемент в матрице проверки четности, m является количеством строк в матрице проверки четности, и d является задержками трубопровода. Когда вы выбираете параметр Enable multiple code rates, d равняется 26. В противном случае d равняется 18.

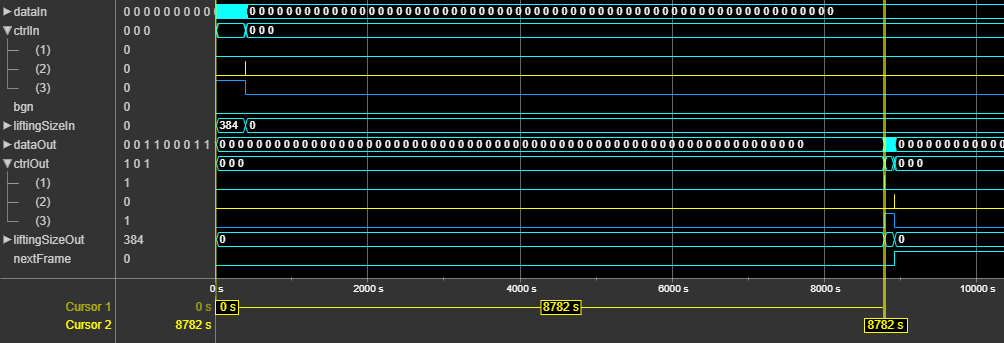

Этот рисунок показывает демонстрационный выход блока NR LDPC Decoder с задержкой. В этом случае bgn и значения входного порта liftingSize установлены в 0 и 384, соответственно, и параметр Number of iterations устанавливается на 8. Задержка блока является 8 782 тактами.

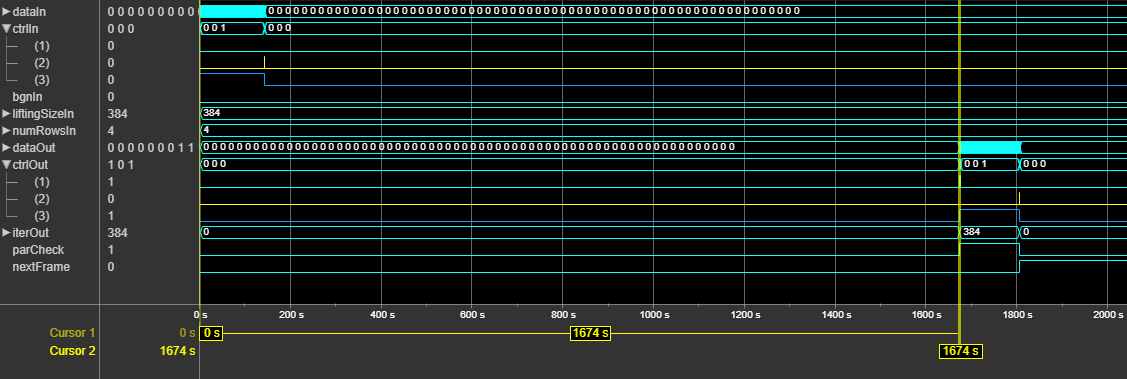

Этот рисунок показывает демонстрационный выход блока NR LDPC Decoder с задержкой. В этом случае bgn, liftingSize и значения входного порта numRows установлены в 0, 384, и 4, соответственно, и параметр Number of iterations устанавливается на 8. Задержка блока является 1 674 тактами.

Пропускная способность блока вычисляется как (cwLen / latency) x f максимум. В этом вычислении:

cwLen является длиной кодовой комбинации, которая равна k b x Z, где k b является 22 для значения bgn 0 и 10 для значения bgn 1.

latency является задержкой блока для заданной настройки

fmax является максимальной рабочей частотой

Для получения дополнительной информации о вычислении задержки, смотрите Задержку. Для получения дополнительной информации о максимальной рабочей частоте, смотрите Эффективность.

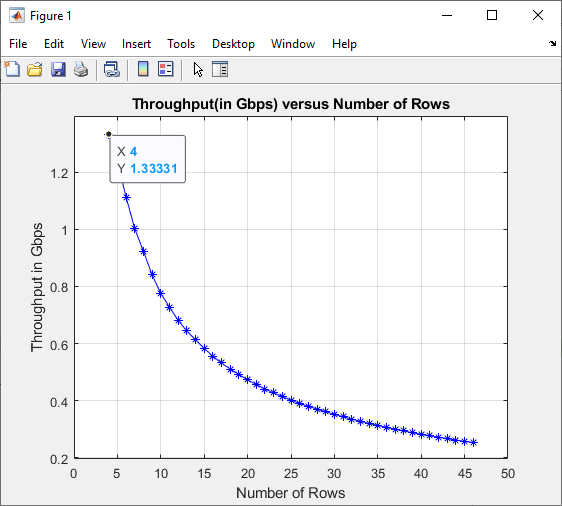

Этот график показывает пропускную способность по сравнению с количеством строк, заданных во входе блока, когда вы устанавливаете параметр Algorithm на Min-sum, параметр Number of iterations к 8, и входной порт bgn к 0.

Эффективность синтезируемого HDL-кода меняется в зависимости от вашей цели и опций синтеза. Это также варьируется на основе типа алгоритма и размера слова значений входа LLR.

Эта таблица показывает результаты синтеза данных ресурсов и данных о производительности блока, когда вы устанавливаете параметр Algorithm на Min-sum, установите параметр Number of iterations на 8, и задайте значения входа LLR типа данных fixdt(1,4,0). Сгенерированный HDL предназначен к Xilinx® Zynq®Ультрамасштабируйте оценочную плату +™ RFSoC.

| Входные данные | Срез LUTs | Регистры среза | Блокируйте RAM | Максимальная частота в МГц |

|---|---|---|---|---|

| Скаляр | 45461 | 58331 | 192.5 | 291 |

| Вектор | 67410 | 75217 | 128.5 | 291.5 |

Эта таблица показывает результаты синтеза данных ресурсов и данных о производительности блока для векторного входа, когда вы устанавливаете параметр Algorithm на Min-sum, установите параметр Decoding termination criteria на Max, установите параметр Number of iterations на 8, выберите параметр Enable multiple code rates и задайте значения входа LLR типа данных fixdt(1,4,0). Сгенерированный HDL предназначен к Xilinx ZynqUltrascale + оценочная плата RFSoC.

| Срез LUTs | Регистры среза | Блокируйте RAM | Максимальная частота в МГц |

|---|---|---|---|

| 72527 | 76002 | 128.5 | 264.2 |

[1] 3GPP TS 38.212. “NR; мультиплексирование и кодирование канала”. Проект партнерства третьего поколения; сеть радиодоступа Technical Specification Group.

[2] Gallager, R. “Имеющие малую плотность Коды с проверкой четности”. Транзакции IEEE на Теории информации 8, № 1 (январь 1962): 21–28. www.doi.org/10.1109/TIT.1962.1057683.

Этот блок поддерживает генерацию кода C/C++ для Simulink® акселератор и быстрые режимы Accelerator и для генерации компонента DPI.

HDL Coder™ обеспечивает дополнительные параметры конфигурации, которые влияют на реализацию HDL и синтезируемую логику.

Этот блок имеет одну, архитектуру HDL по умолчанию.

| ConstrainedOutputPipeline | Количество регистров, чтобы поместить при выходных параметрах путем перемещения существующих задержек в рамках проекта. Распределенная конвейеризация не перераспределяет эти регистры. |

| InputPipeline | Количество входных настроек канала связи, чтобы вставить в сгенерированный код. Распределенная конвейеризация и ограниченная выходная конвейеризация могут переместить эти регистры. |

| OutputPipeline | Количество выходных настроек канала связи, чтобы вставить в сгенерированный код. Распределенная конвейеризация и ограниченная выходная конвейеризация могут переместить эти регистры. |

Вы не можете сгенерировать HDL для этого блока в Resettable Synchronous Subsystem (HDL Coder).

1. Если смысл перевода понятен, то лучше оставьте как есть и не придирайтесь к словам, синонимам и тому подобному. О вкусах не спорим.

2. Не дополняйте перевод комментариями “от себя”. В исправлении не должно появляться дополнительных смыслов и комментариев, отсутствующих в оригинале. Такие правки не получится интегрировать в алгоритме автоматического перевода.

3. Сохраняйте структуру оригинального текста - например, не разбивайте одно предложение на два.

4. Не имеет смысла однотипное исправление перевода какого-то термина во всех предложениях. Исправляйте только в одном месте. Когда Вашу правку одобрят, это исправление будет алгоритмически распространено и на другие части документации.

5. По иным вопросам, например если надо исправить заблокированное для перевода слово, обратитесь к редакторам через форму технической поддержки.