Конкатенации до 128 входных слов в один вывод

HDL Coder / Логика и Битовые операции

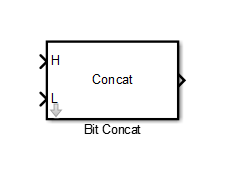

Блок Bit Concat конкатенирует до 128 входных слов в один вывод. Входной порт маркировал L, определяет входное слово самое низкоуровневое. Порт маркировал H, определяет входное слово самого высокого порядка. Справа налево упорядоченное расположение слов в выводе следует за низким-к-высокому упорядоченным расположением входных сигналов.

То, как блок действует, зависит от номера и размерностей входных параметров, можно следующим образом:

Один вход: вход является скаляром или вектором. Когда вход является вектором, кодер конкатенирует отдельные векторные элементы.

Два входных параметров: Входные параметры являются любой комбинацией скаляра и вектора. Когда один вход является скаляром, и другой вектор, кодер выполняет скалярное расширение. Каждый векторный элемент конкатенирован со скаляром, и вывод имеет ту же размерность как вектор. Когда оба входных параметров являются векторами, у них должен быть тот же размер.

Три или больше входных параметров (максимум до 128 входных параметров): Входные параметры являются однородно скаляром или вектором. Все векторные входные параметры должны иметь тот же размер.

Number of Inputs: Введите целое число, задающее количество входных сигналов. Количество входных портов блока обновляет, когда вы изменяете Number of Inputs.

Значение по умолчанию: 2

Минимум: 1

Максимум: 128

Убедитесь, что Number of Inputs равен количеству сигналов, которые вы соединяете с блоком. Если блок имеет несвязанные входные параметры, ошибка происходит во время генерации кода.

Блок имеет до 128 входных портов с H, представляющим входное слово самого высокого порядка и L, представляющий входное слово самое низкоуровневое. Максимальный конкатенированный выходной размер слова составляет 128 битов.

Входной параметр: фиксированная точка, целое число (подписанный или без знака), булевская переменная

Вывод : фиксированная точка Без знака или целое число

Этот блок имеет одну, архитектуру HDL по умолчанию.

Количество регистров, чтобы поместить при выходных параметрах путем перемещения существующих задержек в рамках проекта. Распределенная конвейеризация не перераспределяет эти регистры. Значение по умолчанию 0. См. также ConstrainedOutputPipeline.

Количество входных настроек канала связи, чтобы вставить в сгенерированный код. Распределенная конвейеризация и ограниченная выходная конвейеризация могут переместить эти регистры. Значение по умолчанию 0. См. также InputPipeline.

Количество выходных настроек канала связи, чтобы вставить в сгенерированный код. Распределенная конвейеризация и ограниченная выходная конвейеризация могут переместить эти регистры. Значение по умолчанию 0. См. также OutputPipeline.

Бит уменьшает | Бит вращается | Сдвиг разряда | Секционированный микропроцессор