Вращайте входной сигнал позициями двоичного разряда

HDL Coder / Логика и Битовые операции

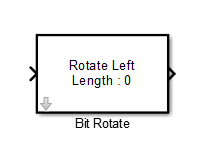

Блок Bit Rotate вращает входной сигнал, левый или правый конкретным количеством позиций двоичного разряда.

Rotate Mode: Задает направление вращения, левого или правого. Значением по умолчанию является Rotate Left.

Rotate Length: Задает количество битов, чтобы вращаться. Задайте значение, больше, чем или равный нулю. Значение по умолчанию 0.

Блок имеет следующие порты:

Поддерживаемые типы данных: фиксированная точка, целое число (подписанный или без знака), булевская переменная

Минимальная битная ширина: 2

Максимальная битная ширина: 128

Имеет совпадающий тип данных как входной сигнал.

Этот блок имеет одну, архитектуру HDL по умолчанию.

Количество регистров, чтобы поместить при выходных параметрах путем перемещения существующих задержек в рамках проекта. Распределенная конвейеризация не перераспределяет эти регистры. Значение по умолчанию 0. См. также ConstrainedOutputPipeline.

Количество входных настроек канала связи, чтобы вставить в сгенерированный код. Распределенная конвейеризация и ограниченная выходная конвейеризация могут переместить эти регистры. Значение по умолчанию 0. См. также InputPipeline.

Количество выходных настроек канала связи, чтобы вставить в сгенерированный код. Распределенная конвейеризация и ограниченная выходная конвейеризация могут переместить эти регистры. Значение по умолчанию 0. См. также OutputPipeline.

Битный Concat | Бит уменьшает | Сдвиг разряда | Секционированный микропроцессор