Возвратите поле последовательных битов от входного сигнала

HDL Coder / Операции HDL

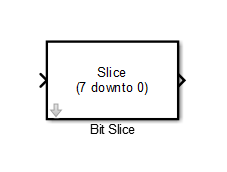

Блок Bit Slice возвращает поле последовательных битов от входного сигнала. Задайте более низкие и верхние контуры битового поля при помощи основанных на нуле индексов в параметрах MSB Position и LSB Position.

MSB Position

Задает позицию двоичного разряда (основанную на нуле) из старшего значащего бита (MSB) поля, чтобы извлечь. Значение по умолчанию равняется 7.

Для входного размера слова WS, LSB Position и MSB Position должны удовлетворить следующие ограничения:

WS > MSB Position >= LSB Position >= 0;

Размер слова вывода вычисляется as (MSB Position - LSB Position) + 1.

LSB Position

Задает позицию двоичного разряда (основанную на нуле) из младшего значащего бита (LSB) поля, чтобы извлечь. Значение по умолчанию 0.

Блок имеет следующие порты:

Поддерживаемые типы данных: фиксированная точка, целое число (подписанный или без знака), булевская переменная

Максимальная битная ширина: 128

Поддерживаемые типы данных: фиксированная точка без знака или беззнаковое целое.

Этот блок имеет одну, архитектуру HDL по умолчанию.

Количество регистров, чтобы поместить при выходных параметрах путем перемещения существующих задержек в рамках проекта. Распределенная конвейеризация не перераспределяет эти регистры. Значение по умолчанию 0. См. также ConstrainedOutputPipeline.

Количество входных настроек канала связи, чтобы вставить в сгенерированный код. Распределенная конвейеризация и ограниченная выходная конвейеризация могут переместить эти регистры. Значение по умолчанию 0. См. также InputPipeline.

Количество выходных настроек канала связи, чтобы вставить в сгенерированный код. Распределенная конвейеризация и ограниченная выходная конвейеризация могут переместить эти регистры. Значение по умолчанию 0. См. также OutputPipeline.

Битный Concat | Бит уменьшает | Бит вращается | Сдвиг разряда