Выберите между несколькими входными параметрами блока (HDL Coder)

Многопортовый блок switch доступен с Simulink®.

Для получения информации о поведении симуляции и параметрах блоков, смотрите Многопортовый Переключатель.

Этот блок имеет одну, архитектуру HDL по умолчанию.

Количество регистров, чтобы поместить при выходных параметрах путем перемещения существующих задержек в рамках проекта. Распределенная конвейеризация не перераспределяет эти регистры. Значение по умолчанию 0. См. также ConstrainedOutputPipeline.

Количество входных настроек канала связи, чтобы вставить в сгенерированный код. Распределенная конвейеризация и ограниченная выходная конвейеризация могут переместить эти регистры. Значение по умолчанию 0. См. также InputPipeline.

Количество выходных настроек канала связи, чтобы вставить в сгенерированный код. Распределенная конвейеризация и ограниченная выходная конвейеризация могут переместить эти регистры. Значение по умолчанию 0. См. также OutputPipeline.

Задайте, сопоставить ли блоки в вашем проекте к inherit, Max, Min или Zero для оператора с плавающей точкой. Значением по умолчанию является inherit. См. также LatencyStrategy.

Этот блок поддерживает генерацию кода для комплексных сигналов.

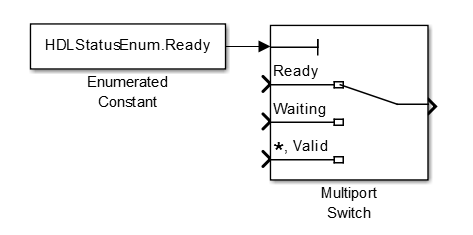

Можно установить Data port order на Specify indices и ввести перечислимые величины для Data port indices. Например, можно соединить блок Enumerated Constant с Многопортовым портом управления Переключателя и использовать перечислимые типы в качестве индексов порта данных.