Преобразуйте векторный сигнал в скалярные или меньшие векторы

HDL Coder / Операции HDL

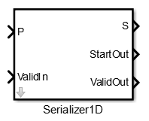

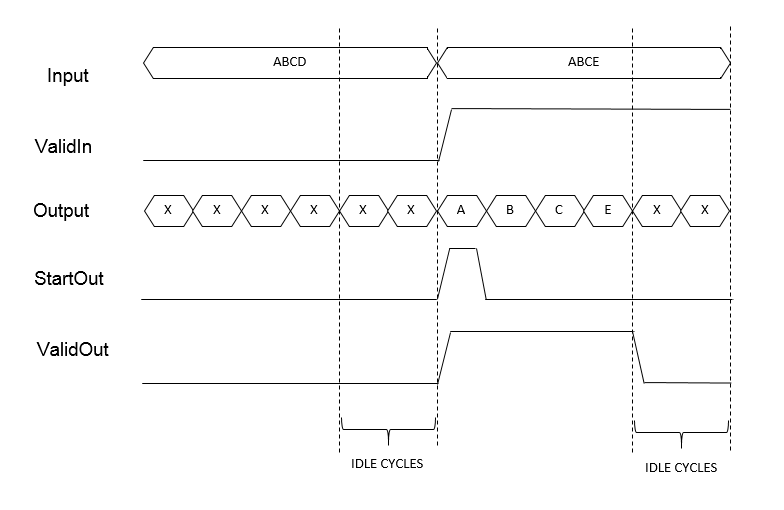

Блок Serializer1D преобразовывает более медленный векторный сигнал в более быстрый поток скалярных сигналов или меньших сигналов вектора размера на основе значений Idle Cycle и Ratio. Чтобы совпадать с быстрее сериализированным выводом, шаг расчета изменяется согласно этому уравнению:

Рассмотрите этот пример, где входные данные являются вектором размера 4, и Ratio установлен в 4.

Выходные данные сериализируют каждый из векторных сигналов в четыре скалярных сигнала. Шаг расчета при выводе: .

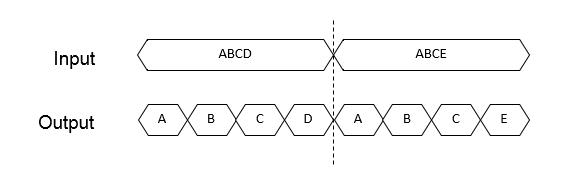

Чтобы добавить неактивные циклы в конце каждого вывода, для Idle Cycles, задают целое число, больше, чем нуль. Рассмотрите этот пример с набором Ratio к 4 и набором Idle Cycles к 2.

Для каждого медленного векторного сигнала вывод имеет шесть быстрых циклов, состоящих из четырех сериализированных скалярных сигналов и двух неактивных циклов. Шаг расчета при выводе .

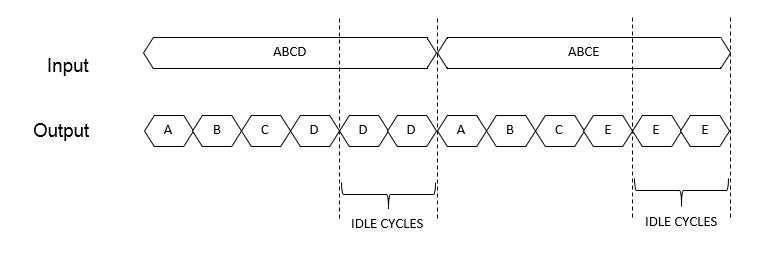

Блок Serializer1D обеспечивает три управляющих сигнала: ValidIn, ValidOut и StartOut. Можно использовать ValidIn, чтобы управлять ValidOut и StartOut. Сериализированный вывод не зависит от ValidIn. Определить, сериализировал ли вывод данные, допустимо, используйте ValidIn и ValidOut. Если вы даете высокий вход ValidIn, и при отсутствии неактивных циклов, ValidOut дает высокую производительность, которая указывает, что сериализированные данные вывода допустимы.

Рассмотрите пример, который имеет входные данные как вектор размера 4, набор Ratio к 4, набор Idle Cycles к 2, и использует все три управляющих сигнала.

Для первого входного вектора, ABCD, ValidIn является ложным. StartOut и ValidOut становятся ложными. Это означает, что значения выходных данных не допустимы. В форме волны значения данных представлены как X, которые соответствуют, чтобы не сделать значений ухода.

Для второго входного вектора, ABCE, ValidIn верен. Выходные данные сериализируют вектор в четыре скалярных сигнала. Управляющий сигнал StartOut становится верным при выводе A, чтобы указать на запуск десериализации. В следующем цикле сигнал StartOut становится ложным. ValidOut верен для всех четырех выходных сигналов, указывающих на допустимые выходные данные для этих четырех циклов. ValidOut становится ложным для неактивных циклов, и значения выходных данных, не заботятся о значениях.

Фактор сериализации, заданный как положительная скалярная величина. Значением по умолчанию является 1.

Отношение равно размеру входного вектора, разделенного на размер выходного вектора. Размер входного вектора должен быть делимым отношением.

Количество неактивных циклов, чтобы добавить в конце каждого вывода. Значением по умолчанию является 0.

Активирует порт ValidIn. Значением по умолчанию является off.

Активирует порт StartOut. Значением по умолчанию является off.

Активирует порт ValidOut. Значением по умолчанию является off.

Размер сигнала входных данных. Размер входного вектора должен быть делимым отношением. По умолчанию блок наследовал размер на основе контекста в модели.

Временной интервал между хитами шага расчета или другой соответствующий шаг расчета такой как непрерывный. По умолчанию блок наследовал шаг расчета на основе контекста в модели. Для получения дополнительной информации смотрите Шаг расчета (Simulink).

Тип входного сигнала блока, заданного как auto, real или complex. Значением по умолчанию является auto.

PВходной сигнал, чтобы сериализировать. Типы данных шины не поддержаны.

ValidInСигнал элемента управления вводом. Этот порт доступен, когда вы устанавливаете флажок ValidIn.

Тип данных: булевская переменная

SСериализированный выходной сигнал. Типы данных шины не поддержаны.

StartOutСигнал элемента управления выводом, который указывает, где запустить десериализацию. Можно использовать этот сигнал в качестве входа StartIn к блоку Deserializer1D. Чтобы использовать этот порт, установите флажок StartOut.

Тип данных: булевская переменная

ValidOutСигнал элемента управления выводом, который указывает на допустимый выходной сигнал. Можно использовать этот сигнал в качестве входа ValidIn к блоку Deserializer1D. Этот порт доступен, когда вы устанавливаете флажок ValidOut.

Тип данных: булевская переменная

Для результатов симуляции, которые совпадают со сгенерированным HDL-кодом в панели Решателя диалогового окна Configuration Parameters, снимают флажок для Treat each discrete rate as a separate task. Когда флажок снимается, однозадачный режим включен. Если вы моделируете блок с этим установленным флажком, выходные данные могут обновить в том же цикле, но в сгенерированном HDL-коде, выходные данные обновляются один цикл позже.

Этот блок имеет одну, архитектуру HDL по умолчанию.

Количество регистров, чтобы поместить при выходных параметрах путем перемещения существующих задержек в рамках проекта. Распределенная конвейеризация не перераспределяет эти регистры. Значение по умолчанию 0. См. также ConstrainedOutputPipeline.

Количество входных настроек канала связи, чтобы вставить в сгенерированный код. Распределенная конвейеризация и ограниченная выходная конвейеризация могут переместить эти регистры. Значение по умолчанию 0. См. также InputPipeline.

Количество выходных настроек канала связи, чтобы вставить в сгенерированный код. Распределенная конвейеризация и ограниченная выходная конвейеризация могут переместить эти регистры. Значение по умолчанию 0. См. также OutputPipeline.