Определенные шаблоны или комбинация блоков с регистрами могут улучшить достижимую частоту часов и уменьшать использование области на платах FPGA. Адаптивная оптимизация конвейеризации создает эти шаблоны путем вставки конвейерных регистров в блоки в проекте. Чтобы определить оптимальное количество конвейерных регистров, чтобы вставить в ваш проект, оптимизация рассматривает целевое устройство, целевую частоту, размеры слова множителя и настройки в HDL Block Properties.

Для HDL Coder™, чтобы вставить адаптивные конвейеры, задайте целевое устройство. Когда ваш проект будет иметь множители, задайте целевое устройство и целевую частоту.

Убедитесь, что балансировка задержки включена для подсистемы, для которой вы хотите, чтобы HDL Coder вставил адаптивные конвейеры. Если вы отключаете балансировку задержки, генератор кода не вставляет адаптивные конвейеры.

Убедитесь, что ваш проект не имеет типов данных с плавающей точкой или операций.

При помощи конвейеризации тактовой частоты с адаптивной конвейеризацией HDL Coder вставляет конвейеры на более быстрой тактовой частоте вместо более медленной скорости передачи данных. С конвейеризацией тактовой частоты лучшая практика состоит в том, чтобы разработать ваш DUT на одном уровне, и затем задать Oversampling factor.

При помощи разделения ресурсов с адаптивной конвейеризацией HDL Coder совместно использует ресурсы и вставляет конвейерные регистры, который сохраняет область и синхронизацию.

В некоторых случаях, когда у вас есть блоки в обратной связи, адаптивная конвейеризация не может вставить необходимое количество конвейерных регистров при выводе. Задержитесь балансировка может затем перестать работать.

Адаптивная конвейеризация поддерживает эти интерполяционные таблицы, множители, умножьтесь, накапливаются, и блоки перехода уровня для автоматической конвейерной вставки.

Интерполяционная таблица n-D

Прямая интерполяционная таблица (n-D)

Оптимизированный HDL синуса

Оптимизированный HDL косинуса

Субдискретизировать

Переход уровня

Продукт

Усиление

Умножьтесь - Добавляют

Умножьтесь - Накапливаются

Интерполяционные таблицы являются блоками в библиотеке HDL Coder> Lookup Tables включая Оптимизированный HDL Синуса и HDL Косинуса Оптимизированные блоки.

Вставить адаптивные конвейеры для блоков интерполяционной таблицы:

Задайте целевое устройство.

Убедитесь, что Interpolation method установлен в Flat.

При генерации кода HDL Coder вставляет регистр без сброса при выводе интерполяционной таблицы. Комбинация блока интерполяционной таблицы и регистра без сброса может потенциально сопоставить с блоками RAM на FPGA.

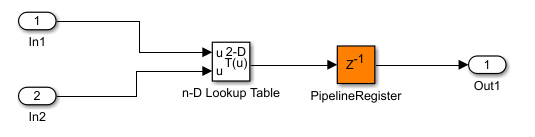

Эта фигура является сгенерированной моделью для n-D блока Lookup Table с Xilinx® Virtex5 как целевое устройство FPGA.

Вставить адаптивные конвейеры для этих блоков:

Задайте целевое устройство.

Задайте целевую частоту, больше, чем нуль.

При генерации кода HDL Coder вставляет регистры в портах ввода и вывода блоков. Комбинация множителей с регистрами может потенциально сопоставить с модулями DSP на целевом устройстве.

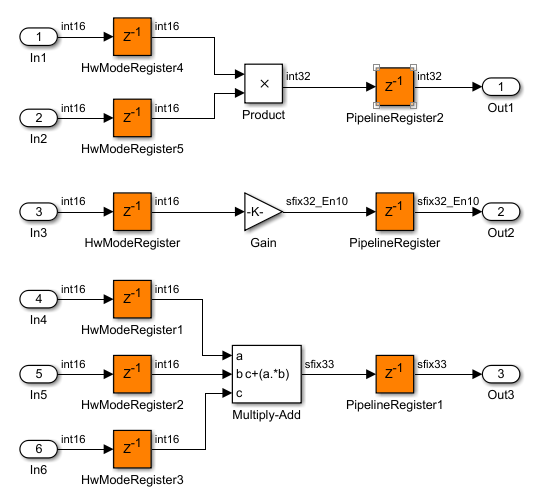

Эта фигура является сгенерированной моделью для продукта, Усиления, и Умножьтесь - Добавляют блоки с Altera® Arria10 как целевое устройство FPGA и целевая частота 500 МГц. Входные параметры к блокам имеют тип int16.

Шаблон и количество конвейера указывают тот HDL Coder, вставки могут отличаться в зависимости от целевого устройства, целевой частоты и размеров слова множителя.

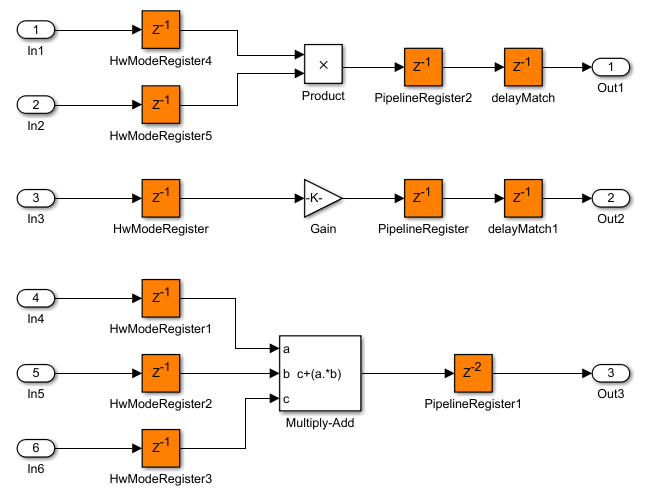

Эта фигура является сгенерированной моделью для блоков с Xilinx Virtex5 как целевое устройство FPGA и целевая частота 1 500 МГц. Входные параметры имеют тип int8.

Блоки имеют различное количество конвейерных регистров в выходных портах. Чтобы совпадать с задержками, HDL Coder добавляет задержку при выводе блоков Усиления и продукта.

Вставить адаптивные конвейеры для Перехода Уровня и Субдискретизировать блоки:

Задайте целевое устройство.

Убедитесь, что Субдискретизируют блоки, имеют Downsample factor, больше, чем два.

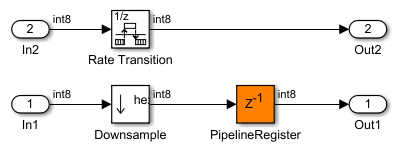

При генерации кода HDL Coder вставляет конвейерный регистр в выходном порту блока Downsample. Сложение конвейерного регистра может избежать обходной логики регистра, которая сохраняет область на целевом FPGA.

Эта фигура является сгенерированной моделью для блоков с Xilinx Virtex5 как целевое устройство FPGA.

Можно установить адаптивную конвейеризацию для целой модели или для более прекрасного управления, можно установить адаптивную конвейеризацию для подсистем в подсистеме DUT верхнего уровня. По умолчанию адаптивная конвейеризация включена на образцовом уровне.

Можно отключить адаптивную конвейеризацию одним из следующих способов:

В HDL Workflow Advisor, на вкладке HDL Code Generation> Set Code Generation Options> Set Optimization Options> Pipelining, выбирают Adaptive pipelining.

В диалоговом окне Configuration Parameters, на вкладке HDL Code Generation> Target and Optimizations> Pipelining, выбирают Adaptive pipelining

В командной строке используйте makehdl или функцию hdlset_param, чтобы установить Адаптивную конвейеризацию на off.

Если вы хотите, чтобы HDL Coder выборочно отключил адаптивные конвейеры для подсистемы в вашей модели, установите AdaptivePipelining на off для той подсистемы.

Чтобы изучить, как установить адаптивную конвейеризацию для подсистемы, смотрите Набор Адаптивная Конвейеризация Для Подсистемы.

Чтобы видеть, что адаптивное конвейерно обрабатывает информацию в отчете, прежде чем вы сгенерируете код для каждой подсистемы или модели - ссылки, включают отчет Генерации кода. Чтобы включить отчет Генерации кода, в диалоговом окне Configuration Parameters, на панели HDL Code Generation, включают Generate optimization report.

Когда вы генерируете код, HDL Coderproduces отчет Генерации кода. В отчете выберите раздел Adaptive Pipelining отчета Оптимизации.

Адаптивный отчет Конвейеризации отображает состояние адаптивной оптимизации конвейеризации и вставил ли HDL Coder адаптивные конвейеры в ваш проект.

Если адаптивная конвейеризация успешна, отчет отображает блоки, для которых HDL Coder вставил конвейерные регистры, количество конвейерных регистров, вставленных, и любые дополнительные примечания. Щелкните по ссылке к блоку, чтобы видеть конвейерные регистры, вставленные в блоки в вашем проекте.

Если адаптивная конвейеризация перестала работать, отчет отображает критерий, который заставил адаптивную конвейеризацию перестать работать.