Можно задать пользовательские платы и пользовательские исходные проекты так, чтобы они были доступны как опции целевого компьютера в рабочем процессе SoC. Пользовательские платы и пользовательские исходные проекты используют ту же систему, которую HDL Coder™ использует для предопределенной платы и целей исходного проекта.

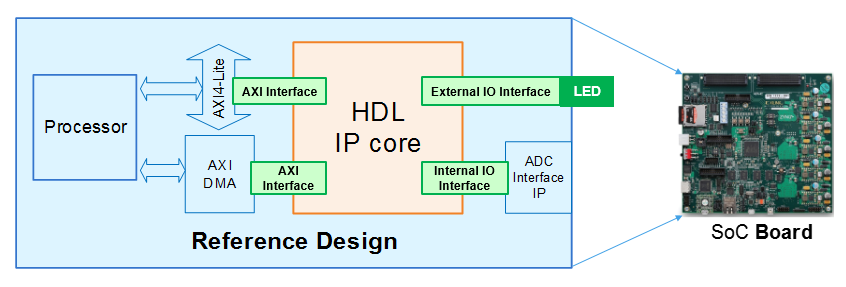

reference design является проектом встраиваемой системы, с которым объединяется ваше сгенерированное ядро IP. board является платформой SoC.

Для пользовательской платы или пользовательского исходного проекта, можно задать различные виды интерфейсов:

Интерфейс AXI: интерфейс между вашим сгенерированным ядром IP и интерфейс AXI4 или AXI4-Lite.

Внешний интерфейс IO: интерфейс между вашим сгенерированным ядром IP и внешний интерфейс.

Внутренний интерфейс IO: интерфейс между вашим сгенерированным ядром IP и другим ядром IP в исходном проекте.

После того, как вы интегрируете свой исходный проект и ядро IP в дизайн-проекте встраиваемой системы, можно программировать плату с проектом встраиваемой системы.

Чтобы задать и указать плату, у вас должны быть board definition, board plugin и board registration file.

Определением платы является файл, который задает характеристики платы. Можно задать больше чем одну пользовательскую плату.

Плагин платы является папкой пакета, которая содержит:

Определение платы.

Все плагины исходного проекта, которые сопоставлены с платой.

Плагин платы имеет одно определение платы, но может иметь несколько исходных проектов.

Файл регистрации плат всегда называют hdlcoder_board_customization.m и содержит список плагинов платы. На вашем пути MATLAB® может быть несколько файлов регистрации плат, но плагин платы не может быть перечислен больше чем в одном файле регистрации плат.

Когда HDL Workflow Advisor открывается, он ищет путь MATLAB файлы с именем hdlcoder_board_customization.m и использует информацию, чтобы заполнить опции требуемой платы. Интерфейсы вы добавляете и задаете для платы, появляются как опции в выпадающем списке Target Platform Interface.

Чтобы задать и указать исходный проект, у вас должны быть reference design definition, reference design plugin и reference design registration file.

Определением исходного проекта является файл, который задает характеристики исходного проекта, включая его связанную плату и интерфейсы. Можно задать несколько пользовательских исходных проектов на плату.

Плагин исходного проекта является папкой пакета, которая содержит:

Определение исходного проекта.

Файлы, которые являются частью дизайн-проекта встраиваемой системы и характерны для вашего стороннего инструмента синтеза, включая Tcl, проект, и разрабатывают файлы.

Плагин исходного проекта имеет одно определение исходного проекта и сопоставлен с одной платой.

Регистрационный файл исходного проекта всегда называют hdlcoder_ref_design_customization.m и содержит список плагинов исходного проекта для определенной платы. Может быть несколько регистрационных файлов исходного проекта для определенной платы на вашем пути MATLAB, но плагин исходного проекта не может быть перечислен больше чем в одном регистрационном файле плагина исходного проекта.

Когда HDL Workflow Advisor открывается, он ищет путь MATLAB файлы с именем hdlcoder_ref_design_customization.m и использует информацию, чтобы заполнить опции исходного проекта для каждой платы. Интерфейсы вы добавляете и задаете для исходного проекта, появляются как опции в выпадающем списке Target Platform Interface.

Для примеров рабочей платы и определений исходного проекта, обратитесь к предопределенному Altera® SoC и плагинам платы Xilinx® Zynq®, которые включают предопределенные плагины исходного проекта:

support_package_installation_folder /toolbox/hdlcoder/supportpackages/zynq7000/+ZedBoard/

support_package_installation_folder /toolbox/hdlcoder/supportpackages/zynq7000/+ZynqZC702/

support_package_installation_folder /toolbox/hdlcoder/supportpackages/alterasoc/+AlteraCycloneV/

support_package_installation_folder /toolbox/hdlcoder/supportpackages/alterasoc/+ArrowSoCKit/

hdlcoder.Board | hdlcoder.ReferenceDesign