Используйте HDL import, чтобы импортировать синтезируемый HDL-код в среду моделирования Simulink®. HDL import анализирует файл входа HDL и генерирует модель Simulink. Модель является средой блок-схемы, которая визуально представляет HDL-код с точки зрения функциональности и поведения.

Путем импорта HDL-кода в Simulink вы можете:

Отладьте свой проект HDL в основанной на модели среде симуляции. Чтобы отладить внутренние сигналы, определяйте сигналы как тестовые точки и включите генерацию порта HDL DUT для сигналов тестовой точки. Когда вы генерируете код, HDL Coder™ распространяет сигналы к верхнему уровню вашей модели Simulink.

Улучшите область и синхронизацию вашего проекта на целевом компьютере при помощи скорости образцового уровня и блочного уровня и оптимизации области, такой как разделение ресурсов и распределенная конвейеризация.

Разверните проект на FPGA и платформах SoC при помощи Generic ASIC/FPGA и рабочих процессов IP Core Generation в HDL Workflow Advisor.

Проверьте функциональность проекта HDL путем генерации модели валидации или испытательного стенда HDL. Если у вас есть HDL Verifier™, можно проверить проект при помощи Cosimulation, испытательного стенда SystemVerilog DPI или FPGA-in-the-Loop.

Чтобы сгенерировать модель Simulink, убедитесь, что файл HDL вы импортируете:

Свободно от синтаксических ошибок.

Является синтезируемым.

Использование поддержало построения Verilog® для импорта.

Чтобы импортировать HDL-код, в Командном окне MATLAB®, запускают функцию importhdl. Например, чтобы импортировать файл Verilog example.v, в командной строке, введите:

importhdl('example.v')Построения, которые вы используете в HDL-коде, могут вывести простые блоки Simulink те, которые Добавляют и продукт к блокам RAM, таким как Двойной Уровень Двухпортовый RAM. Для примеров, которые иллюстрируют различные модели Simulink, которые выведены, смотрите importhdl.

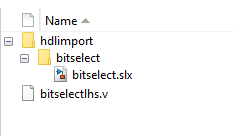

Сгенерированную модель Simulink называют в честь главного модуля в файле входа HDL, который вы задаете. Модель сохранена в пути hdlimport/TopModule относительно текущей рабочей папки. Например, если вы вводите файл с именем bitselectlhs.v к функции importhdl, которая имеет bitselect как главное имя модуля, сгенерированная модель Simulink имеет имя bitselect.slx и сохранена в пути hdlimport/bitselect относительно текущей папки.

Когда вы запускаете функцию importhdl, импорт HDL проверяет синтаксис и семантику входного HDL-кода. Семантическая верификация проверяет на построения инстанцирования модуля, неиспользуемые порты в определении модуля, списке чувствительности блока always, и так далее. Если импорт HDL перестал работать, генератор кода предоставляет сообщение об ошибке и ссылку на имя файла и номер строки.

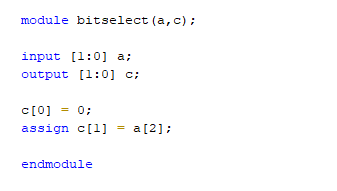

Например, рассмотрите этот код Verilog для модуля bitselect:

Когда вы запускаете функцию importhdl, импорт HDL генерирует сообщение об ошибке:

Parser Error: bitselectlhs.v:6:2: error: Syntax Error near '['..

Сообщение об ошибке указывает, что существует синтаксическая ошибка в строке 6. Чтобы зафиксировать эту ошибку, измените синтаксис на оператор присваивания.

assign c[0] = 0;