verifyМожно сгенерировать компонент SystemVerilog DPI от

операторов Simulink® Test™ verify. При использовании Тестовых блоков Последовательности Оценки или Теста можно оценить поведение модели включением операторов verify в тестовой последовательности. Чтобы сопоставить операторы verify с утверждением SystemVerilog, сгенерируйте компонент SystemVerilog DPI от блока Test Assessment или Test Sequence. Используйте компонент SystemVerilog DPI в своей тестовой среде HDL.

В Simulink создайте модель для устройства под тестом (DUT) и создайте испытательный стенд для модели с помощью Тестовых блоков Последовательности Оценки или Теста. Используйте Тестовый Редактор Последовательности (Simulink Test), чтобы создать и отредактировать тестовые шаги. В тестовой последовательности используйте операторы verify, чтобы оценить симуляцию, как описано в Тестовом Синтаксисе Последовательности и Оценки (Simulink Test).

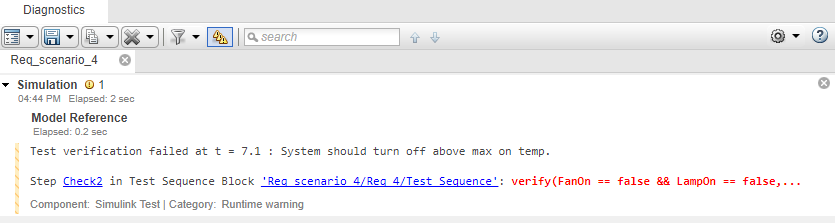

При симуляции проекта в Simulink симуляция испускает предупреждение, если оценка verify перестала работать.

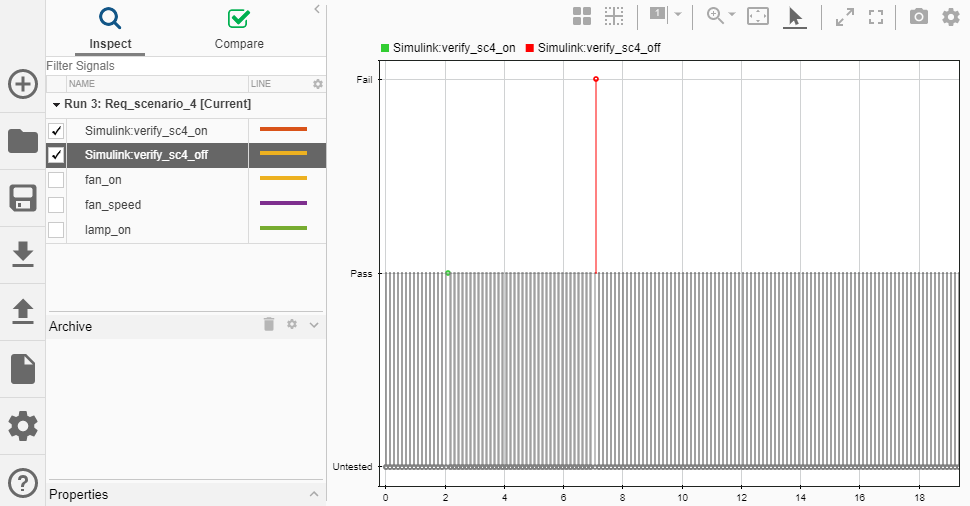

Можно просмотреть и осмотреть результаты симуляции при помощи Simulation Data Inspector. Откройте Инспектора Данных моделирования путем ввода этого кода в командной строке MATLAB®.

Simulink.sdi.view

verifyВ диалоговом окне Configuration Parameters выберите Code Generation на левой панели. Под Target Selection, набор System Target File к systemverilog_dpi_grt.tlc, или альтернативно к systemverilog_dpi_ert.tlc при использовании Embedded Coder®.

Выберите SystemVerilog DPI на левой панели. Под SystemVerilog Ports, набор тип данных и настройки подключения. Нажмите OK.

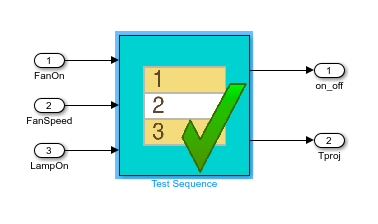

Чтобы сгенерировать Компонент DPI, блок Test Assessment или блок Test Sequence должны быть в Подсистеме Simulink.

В Simulink щелкните правой кнопкой по блоку подсистемы, который содержит тестовую последовательность, и выберите C/C++ Code> Build This Subsystem. Нажмите Build в диалоговом окне, которое открывается.

Альтернатива командной строки: Используйте функцию rtwbuild, чтобы создать систему. Например, чтобы создать подсистему по имени "My_verify_tst", введите этот код в командной строке MATLAB.

rtwbuild('My_verify_tst');Измените свою текущую папку на папку dpi_tb, которая находится под папкой генерации кода в вашей установке симулятора HDL. Запустите свой симулятор HDL и запустите сгенерированный скрипт, чтобы запустить симуляцию. Симуляция вывод сопоставима с Simulink вывод.

Для получения дополнительной информации о выполнении симуляции HDL смотрите, Проверяют Сгенерированный Компонент По Данным Simulink.

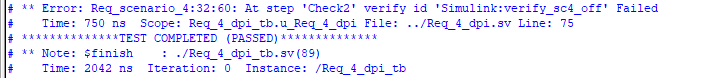

После выполнения симуляции SystemVerilog со сгенерированной тестовой последовательностью ваш файл журнала выводит предупреждения и ошибки. Чтобы идентифицировать, какой блок породил определенное предупреждение или вывод ошибок, используйте Идентификатор Simulink (SID) функция hilite.

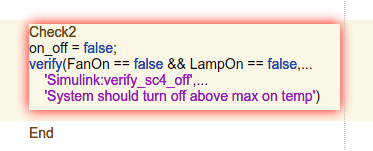

Каждая сгенерированная ошибка или предупреждение отображений уникальное имя, идентифицирующее его источник. Тот номер является SID того блока. Например, вывод в предыдущей фигуре показывает ошибку, которая была сгенерирована тестовым блоком последовательности с SID Req_scenario_4:32:60.

# ** Error: Req_scenario_4:32:60: At step 'Check2' verify id 'Simulink:verify_sc4_off' Failed

Чтобы подсветить блок, который сгенерировал это предупреждение, введите этот код в командной строке MATLAB.

Simulink.ID.hilite('Req_scenario_4:32:60');Фигура подсвечивает и проверять оператор и тестовый блок последовательности, который создал это предупреждение.

Для получения дополнительной информации об Идентификаторах Simulink смотрите, Определяют местоположение Компонентов Схемы Используя Идентификаторы Simulink (Simulink).

По умолчанию сгенерированный компонент DPI выводит ошибку, когда оценка verify тестируется и перестала работать. Чтобы видеть дополнительный вывод, сгенерированный оценкой verify, используйте аргумент +VERBOSE_VERIFY в командной строке симуляции HDL. Этот аргумент добавляет информацию, показывающую, когда оценка verify не была протестирована, и когда это было протестировано и передано. Например, при использовании ModelSim® вводят следующее в командной строке.

vsim -classdebug -c -voptargs=+acc -sv_lib ../Req_4 work.Req_4_dpi_tb +VERBOSE_VERIFY

Эта команда выводит многословный журнал, который включает детали о том, когда оценки verify были протестированы и передали ли они или перестали работать.

У вас может быть несколько шагов в тестовой последовательности, которые используют оценку verify или несколько компонентов DPI, регистрирующих предупреждения от симуляции. В вашей тестовой модели можно отфильтровать сгенерированный вывод для определенных шагов verify путем определения связанного SID как плюс аргумент на командной строке. Например, чтобы выключить весь вывод для SID Req_scenario_4:32:60, введите этот код в командной строке HDL.

vsim -classdebug -c -voptargs=+acc -sv_lib ../Req_4 work.Req_4_dpi_tb +Req_scenario_4:32:60

Протестируйте оценку | Протестируйте последовательность