Создайте модель для этого примера:

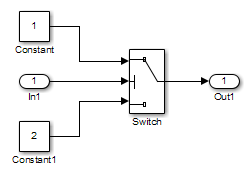

Создайте модель Simulink®.

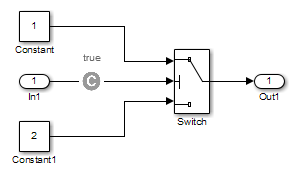

Скопируйте следующие блоки в свое пустое окно модели:

От библиотеки Sources, блок Inport, чтобы инициировать входной сигнал, чье значение средства управления Simulink Design Verifier™.

От библиотеки Sources, два блока Константа, чтобы служить вводами данных блока switch.

От библиотеки Signal Routing, блок switch, чтобы обеспечить простую логику.

От библиотеки Sinks, блок Outport, чтобы получить выходной сигнал.

В вашей модели дважды кликните один из блоков Константа и задайте его параметр Constant value как 2.

Соедините блоки так, чтобы ваша модель казалась подобной следующей схеме.

В окне модели выберите Simulation> Model Configuration Parameters.

На левой стороне диалогового окна Configuration Parameters, в дереве Select, кликают по категории Solver. На правой стороне, под Solver selection:

Установите опцию Type на Fixed-step.

Установите опцию Solver на Discrete (no continuous states).

Simulink Design Verifier анализирует только модели, которые используют решатель фиксированного шага.

Нажмите OK, чтобы сохранить ваши изменения и закрыть диалоговое окно Configuration Parameters.

Сохраните свою модель с именем ex_generate_test_cases_example.

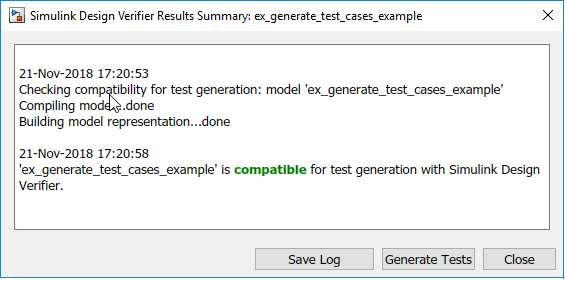

Каждый раз Simulink Design Verifier анализирует модель, прежде чем анализ начнется, программное обеспечение выполняет проверку совместимости. Если ваша модель не совместима, программное обеспечение не может анализировать ее.

Прежде чем вы запустите анализ, можно также убедиться, что модель совместима с программным обеспечением Simulink Design Verifier:

Откройте модель ex_generate_test_cases_example.

В окне модели выберите Analysis> Design Verifier> Check Compatibility> Model.

Программное обеспечение отображает логарифмическое окно, которое утверждает, совместима ли ваша модель для анализа.

Модель, которую вы только создали, совместима.

Если проверка совместимости указывает, что ваша модель частично совместима, ваша модель содержит по крайней мере один объект, который не поддерживает Simulink Design Verifier. Можно анализировать частично совместимую модель, но по умолчанию неподдерживаемые объекты погашены. Результаты анализа могут быть неполными.

Для получения дальнейшей информации об автоматическом блокировании, смотрите Несовместимости Указателя с Автоматическим Блокированием.

Сконфигурируйте Simulink Design Verifier, чтобы сгенерировать тесты, которые достигают 100% Decision Coverage для модели ex_generate_test_cases_example:

Откройте модель ex_generate_test_cases_example.

В окне модели выберите Analysis> Design Verifier> Options.

На левой стороне диалогового окна Configuration Parameters, в дереве Select, кликают по категории Design Verifier. Под Analysis options, набор опция Mode к Test generation.

На левой стороне диалогового окна Configuration Parameters, в дереве Select, кликают по категории Test Generation.

На панели Test Generation, установленной параметр Model coverage objectives на Decision.

В данном примере анализ генерирует тесты та запись только Decision Coverage.

Параметр Test suite optimization устанавливается по умолчанию на CombinedObjectives. Если вы хотите сгенерировать меньше, но более длинные тесты, выберите LongTestcases для параметра Test suite optimization.

Нажмите OK, чтобы сохранить ваши изменения и закрыть диалоговое окно Configuration Parameters.

Сохраните модель ex_generate_test_cases_example.

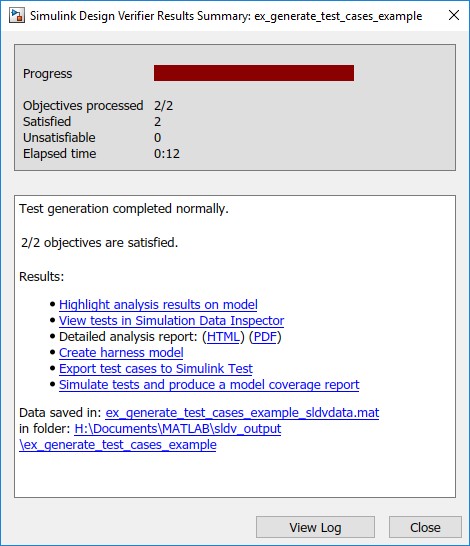

Чтобы анализировать модель ex_generate_test_cases_example, в окне модели, выбирают Analysis> Design Verifier> Generate Tests> Model. Программное обеспечение Simulink Design Verifier начинает анализировать вашу модель, чтобы сгенерировать тесты.

Во время анализа логарифмическое окно показывает прогресс анализа. Это отображает информацию, такую как количество обработанных целей тестирования и какие цели удовлетворены.

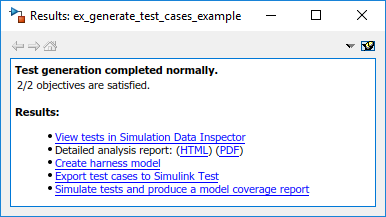

Когда программное обеспечение завершает свой анализ, логарифмическое окно отображает следующие опции для рассмотрения результатов.

Следующие разделы описывают, как можно рассмотреть результаты анализа:

Подсветите результаты анализа на модели в качестве примера:

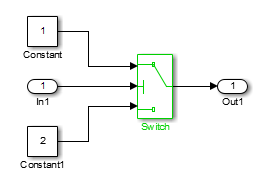

В логарифмическом окне для анализа ex_generate_test_cases_example нажмите Highlight analysis results on model.

Блок switch обрисован в общих чертах в зеленом, который указывает, что блок switch имеет тесты, которые удовлетворяют его цели тестирования.

Окно Simulink Design Verifier Results открывается. Когда вы кликаете по объектам в модели, это окно изменяется на результаты детального анализа отображения для того объекта. По умолчанию окно Simulink Design Verifier Results всегда является самым верхним видимым окном. Чтобы позволить окну перемещаться позади другого окна, щелкните![]() и очиститесь Поверх остальных окон.

и очиститесь Поверх остальных окон.

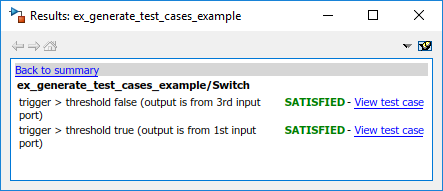

Кликните по подсвеченному блоку switch.

Окно Simulink Design Verifier Results указывает, что анализ сгенерировал тесты для обеих целей тестирования:

trigger > threshold

trigger < threshold

Для получения дополнительной информации о подсвеченных результатах анализа на модели, смотрите Подсвеченные Результаты на Модели.

Создайте подробный аналитический отчет HTML:

В логарифмическом окне Simulink Design Verifier, в отчете Детального анализа, нажимают HTML.

Отчет HTML открывается в окне браузера.

Отчет включает в себя следующий Table of Contents. Кликните по гиперссылке, чтобы перейти к разделу в отчете.

В Table of Contents нажмите Summary, чтобы отобразить Итоговую главу отчета.

Итоговая глава перечисляет информацию о модели и состоянии целей — удовлетворенный или нет.

В Table of Contents нажмите Analysis Information, чтобы отобразить главу информации об Анализе.

Глава информации об Анализе предоставляет информацию о:

Модель, которую вы анализировали.

Опции, которые вы задали для анализа.

Приближения программное обеспечение выполняются во время анализа.

В Table of Contents нажмите Test Objectives Status, чтобы отобразить главу Состояния Целей тестирования отчета.

Эта таблица показывает, что анализ удовлетворил обе цели тестирования, сопоставленные блоком switch в модели ex_generate_test_cases_example, для которой это сгенерировало два теста.

В соответствии со столбцом таблицы Test Case, нажмите 2, чтобы отобразить раздел Test Case 2.

Этот раздел предоставляет подробную информацию о тесте, который анализ сгенерировал, чтобы достигнуть цели в вашей модели. Этот тест достигает цели тестирования 1, когда блок switch передает свой третий вход его выходному порту. А именно, программное обеспечение решает, что значение –1 для управляющего сигнала блока switch заставляет блок передавать свой третий вход как блок вывод.

Для получения дополнительной информации об отчетах HTML, см. Отчеты Simulink Design Verifier.

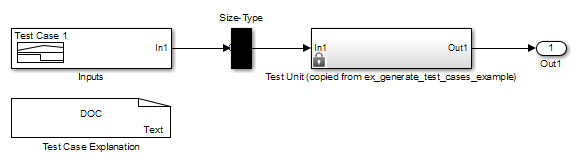

Чтобы создать модель тестовой обвязки с тестами, которые удовлетворяют цели тестирования в вашей модели в логарифмическом окне Simulink Design Verifier, нажимают Create harness model.

Программное обеспечение создает модель тестовой обвязки под названием ex_generate_test_cases_example_harness.

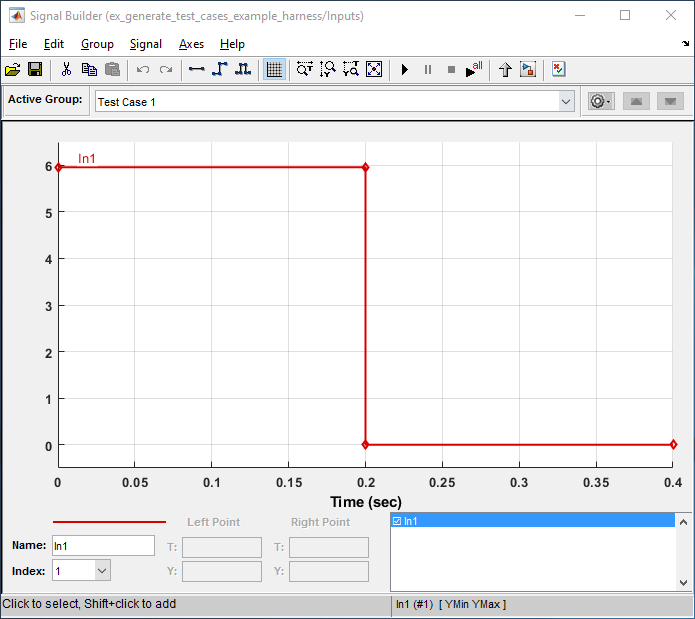

Блок Signal Builder под названием Входные параметры содержит тесты. Дважды кликните блок Inputs, чтобы видеть тесты. От блока Signal Builder можно моделировать модель с помощью тестов и представить отчет покрытия модели, как описано в Моделируют Тесты и Представляют Отчет Покрытия модели.

Для получения дополнительной информации о модели тестовой обвязки, смотрите Модели тестовой обвязки Simulink Design Verifier.

Если Анализ Генерирует Много Тестов. Если у вас есть большая модель, анализ может произвести модель тестовой обвязки, которая содержит большое количество тестов.

Выполнить более эффективный анализ и создать более легкие к анализу результаты:

Установите параметр Test suite optimization на LongTestcases.

Повторно выполните анализ.

В оптимизации LongTestcases анализ генерирует меньше, но более длинные тесты, что каждый удовлетворяет несколько целей тестирования.

Моделировать модель тестовой обвязки с помощью сгенерированных тестов в модели тестовой обвязки:

В модели тестовой обвязки дважды кликните блок Inputs, чтобы открыть диалоговое окно Signal Builder.

В диалоговом окне Signal Builder нажмите Run all![]() .

.

Программное обеспечение моделирует модель тестовой обвязки с помощью и тестов, собирает информацию покрытия модели и отображает отчет покрытия. Отчет покрытия указывает, что тесты записывают 100% Decision Coverage для модели ex_generate_test_cases_example.

Можно также моделировать модель, не создавая модель тестовой обвязки. В логарифмическом окне Simulink Design Verifier нажмите Simulate tests and produce a model coverage report.

Для получения дополнительной информации о покрытии модели, см. Отчет Покрытия модели Верхнего уровня (Simulink Coverage).

sldvDataФайлом данных Simulink Design Verifier является MAT-файл, который содержит структуру под названием sldvData. Эта структура хранит все данные, которые анализ собирает и производит во время анализа. Можно использовать файл данных, чтобы провести собственный анализ или сгенерировать пользовательский отчет.

Чтобы просмотреть файл данных, кликните по имени файла данных в логарифмическом окне, в этом примере, ex_generate_test_cases_example_sldvdata.mat. Когда вы кликаете по имени файла, копия объекта sldvData инстанцируют в рабочей области MATLAB® так, чтобы можно было рассмотреть и управлять данными.

Для получения дополнительной информации о файлах данных Simulink Design Verifier, смотрите Файлы данных Simulink Design Verifier.

Пока ваша модель остается открытой, можно просмотреть результаты нового анализа Simulink Design Verifier в Model Explorer.

В Редакторе Simulink выберите Analysis> Design Verifier > Results> Active. Model Explorer открывается. Результаты последнего анализа Simulink Design Verifier появляются в правой панели.

Для любого анализа Simulink Design Verifier, от Model Explorer, можно выполнить следующие задачи.

| Задача | Для получения дополнительной информации |

|---|---|

Подсветите результаты анализа на модели. | Подсвеченные результаты на модели |

Сгенерируйте отчет детального анализа. | Отчеты Simulink Design Verifier |

Создайте модель тестовой обвязки, или если модель тестовой обвязки уже существует, откройте его. Если никакие тесты не были сгенерированы во время анализа, эта опция не доступна. | Модели тестовой обвязки Simulink Design Verifier |

Просмотрите файл данных. | Файлы данных Simulink Design Verifier |

Просмотрите файл журнала. | Файлы журнала Simulink Design Verifier |

После того, как вы закроете свою модель, вы больше не можете просматривать результаты анализа.

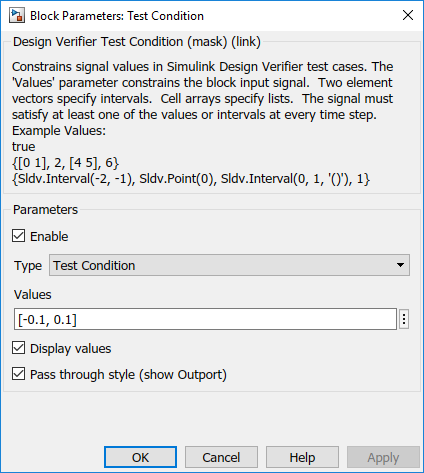

Можно использовать блок Test Condition, чтобы ограничить сигналы в модели к определенным значениям во время анализа.

В подсказке команды MATLAB введите sldvlib, чтобы отобразить библиотеку Simulink Design Verifier.

Откройте подбиблиотеку Objectives и Constraints.

Скопируйте блок Test Condition в свою модель путем перетаскивания его от библиотеки Simulink Design Verifier до окна модели.

В окне модели вставьте блок Test Condition между Inport и Switch blocks.

Дважды кликните блок Test Condition, чтобы получить доступ к его атрибутам.

Диалоговое окно параметров блоков Условия испытания открывается.

В поле Values введите [-0.1, 0.1]. При генерации тестов для этой модели анализ ограничивает значения сигналов, вводя порт управления блока switch в заданную область значений.

Нажмите OK, чтобы сохранить ваши изменения и закрыть диалоговое окно параметров блоков Условия испытания.

Сохраните свою модель как ex_generate_test_cases_with_tc_block и сохраните его открытым.

Анализируйте модель ex_generate_test_cases_with_tc_block с блоком Test Condition. Чтобы наблюдать, как блок Test Condition влияет на генерацию тестов, сравните результат этого анализа к результату, в котором вы получили, Анализируют Модель В качестве примера.

В окне модели выберите Analysis> Design Verifier> Generate Tests> Model.

Программное обеспечение Simulink Design Verifier отображает логарифмическое окно и начинает анализировать вашу модель, чтобы сгенерировать тесты. Когда программное обеспечение завершает анализ, логарифмическое окно отображает опции для рассмотрения результатов.

В логарифмическом окне Simulink Design Verifier нажмите Generate detailed analysis report.

Чтобы начать рассматривать отчет, в Table of Contents, нажимают Summary.

Итоговая глава указывает, что Simulink Design Verifier удовлетворил две цели тестирования в модели.

В Table of Contents нажмите Analysis Information. Прокрутите к нижней части этой главы к разделу Constraints.

Этот раздел перечисляет блок Test Condition, который вы добавили, чтобы ограничить значение управляющего сигнала блока switch к интервалу [–0.1, 0.1].

В Table of Contents нажмите Test Objectives Status.

Эта таблица показывает, что Simulink Design Verifier удовлетворил обе цели тестирования для блока switch через эти два сгенерированные теста.

В соответствии со столбцом таблицы Test Case, нажмите 1.

Этот раздел предоставляет подробную информацию о тесте, который программное обеспечение сгенерировало, чтобы достигнуть цели в вашей модели. Этот тест достигает цели тестирования 1, когда блок switch передает свой третий вход его выходному порту. Несмотря на то, что блок Test Condition ограничивает область входных сигналов к интервалу [–0.1, 0.1], программное обеспечение решает, что значение –0.1 для управляющего сигнала блока switch удовлетворяет эту цель.

Чтобы подтвердить, что тест достигает 100% Decision Coverage, откройте модель тестовой обвязки.

Дважды кликните блок Inputs, чтобы открыть диалоговое окно Signal Builder.

В диалоговом окне Signal Builder нажмите Run all![]() .

.

Программное обеспечение Simulink моделирует модель тестовой обвязки с помощью и тестов, собирает информацию покрытия модели и отображает отчет покрытия. Раздел Summary отчета указывает, что Simulink Design Verifier сгенерировал тесты, которые достигают полного Decision Coverage для вашей модели в качестве примера.

Если анализ производит ошибку The model is contradictory in its current configuration, программное обеспечение обнаружило противоречие в вашей модели и не может анализировать модель.

У вас может быть противоречие, если ваша модель имеет блоки Цели тестирования с неправильными параметрами. Например, противоречие может быть целью, которая утверждает, что сигнал должен быть между 0 и 5, когда сигнал является постоянными 10.

Если программное обеспечение обнаруживает противоречие, все предыдущие результаты делаются недействительным, и программное обеспечение сообщает, что некоторые цели не могут быть удовлетворены.