Сигналы пакета часов состоят из сигналов тактовой частоты, сбросов и сигналов разрешения действии по сигналу тактовой частоты. Во время генерации кода HDL Coder™ создает сигналы пакета часов на основе последовательных элементов, таких как персистентные переменные или блоки Delay, которые вы используете в своем проекте. По умолчанию один основной тактовый генератор и один основной сброс управляют всеми последовательными элементами в вашем проекте.

Если вы используете персистентные переменные в MATLAB®, HDL Coder генерирует сигналы пакета часов. Персистентная переменная является локальной переменной в функции MATLAB, которая сохраняет ее значение в памяти между вызовами функции. Для генерации кода функции должны инициализировать персистентную переменную, если это пусто. Для получения дополнительной информации смотрите persistent.

Рассмотрите этот код MATLAB, который использует персистентную переменную n.

function y = persist_fcn(u) persistent n if isempty(n) n = 1; end y = n; n = n + u; end

Когда вы генерируете код, HDL Coder создает сигналы тактовой частоты, сбросы и сигналы разрешения действии по сигналу тактовой частоты. Эти сигналы называют как clkсброс, и clk_enable в HDL-коде. Чтобы изучить, как сгенерировать HDL-код, смотрите Основную генерацию HDL-кода и Синтез FPGA из MATLAB.

Этот код показывает сгенерированный код Verilog для модели. Чтобы совпадать с MATLAB персистентное переменное поведение, HDL-код использует всегда блок. В положительном ребре сигнала часов, когда сброшенный является низким и разрешать сигнал высок, значение tmp присвоен переменной n после задержки 1 ns.

`timescale 1 ns / 1 ns

module persist_fcn_fixpt

(clk, reset, clk_enable,

u, ce_out, y);

input clk, reset, clk_enable;

input u; // ufix1

output ce_out;

output y; // ufix1

..

assign enb = clk_enable;

assign p4tmp_1 = {1'b0, u};

assign tmp = n + p4tmp_1;

always @(posedge clk or posedge reset)

begin : n_reg_process

if (reset == 1'b1) begin

n <= 2'b01;

end

else begin

if (enb) begin

n <= tmp;

end

end

end

assign y = n[0];

assign ce_out = clk_enable;

endmodule // persist_fcn_fixpt

См. также Персистентные Переменные и Персистентные Переменные типа массив.

Чтобы смоделировать последовательные элементы в Simulink® и сгенерировать часы связывают сигналы, можно использовать различные виды блоков Delay, графиков Stateflow® или персистентных переменных в блоках MATLAB Function или блоках MATLAB System. Генератор кода сопоставляет шаг расчета, который вы задаете на своей модели к тактам в проекте HDL. По умолчанию модель является одним уровнем, что означает, что один модуль шага расчета в Simulink сопоставляет с одним тактом в HDL-коде.

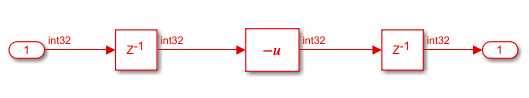

Например, рассмотрите эту модель что выходные параметры унарный минус входа после двух модулей шага расчета. Вход имеет int32 как тип выходных данных.

Когда вы генерируете код, HDL Coder создает сигналы тактовой частоты, сбросы и сигналы разрешения действии по сигналу тактовой частоты. Эти сигналы называют как clkсброс, и clk_enable в HDL-коде. Чтобы изучить, как сгенерировать код, смотрите, Генерируют HDL-код из Модели Simulink.

Этот код показывает сгенерированный код Verilog для модели. Чтобы совпадать с поведением блока Simulink Delay, HDL-код использует всегда блок для каждого блока Delay. В положительном ребре сигнала часов, когда сброшенный является низким и разрешать сигнал высок, вход передается выходу после единичной задержки. Один всегда блок задерживает вход 1 ns прежде, чем вычислить унарное минус. Другой всегда блокируются, вычисляет унарное минус после 1 ns.

`timescale 1 ns / 1 ns

module unary_minus

(clk, reset, clk_enable,

In1, ce_out, Out1);

input clk, reset, clk_enable;

input signed [31:0] In1; // int32

output ce_out;

output signed [31:0] Out1; // int32

...

assign enb = clk_enable;

always @(posedge clk or posedge reset)

begin : Delay_process

if (reset == 1'b1) begin

Delay_out1 <= 32'sb0;

end

else begin

if (enb) begin

Delay_out1 <= In1;

end

end

end

...

always @(posedge clk or posedge reset)

begin : Delay2_process

if (reset == 1'b1) begin

Delay2_out1 <= 32'sb0;

end

else begin

if (enb) begin

Delay2_out1 <= Unary_Minus_out1;

end

end

end

...

endmodule // unary_minus

Если вы используете различные шаги расчета в своей модели или включаете скорость и оптимизацию области, модель становится многоскоростной. Чтобы узнать о генерации пакета часов от многоскоростных моделей, смотрите Генерацию кода от Многоскоростных моделей.