HDL Workflow Advisor проводит вас по этапам генерации HDL-кода для подсистемы Simulink® и процесса проектирования FPGA, таким как:

Проверка модели для совместимости генерации HDL-кода и автоматически фиксация несовместимых настроек.

Генерация HDL-кода, испытательного стенда и скриптов, чтобы создать и запустить код и испытательный стенд.

Генерация cosimulation или испытательных стендов SystemVerilog DPI и покрытия кода (требует HDL Verifier™).

Синтез и анализ синхронизации посредством интеграции со сторонними инструментами синтеза.

Обратная корректировка проекта модели с информацией о критическом пути и другой информацией получена во время синтеза.

Полные автоматизированные рабочие процессы для выбранных целевых устройств разработки FPGA, включая FPGA в симуляции цикла (требует HDL Verifier), и рабочий процесс ввода-вывода FPGA Simulink Real-Time™.

Выбрать испытательный стенд и опции покрытия кода для генерации HDL-кода из модели Simulink с помощью HDL Workflow Advisor:

Выполните шаги настройки в генерации HDL-кода и Синтезе FPGA из Модели Simulink.

На Шаге 3.1.4 HDL Workflow Advisor, Set Testbench Options, избранного испытательного стенда и опций покрытия кода от раздела Test Bench Generation Output. Кодер генерирует build-run скрипт для вашего испытательного стенда и Simulation tool, который вы задаете. Если вы выбираете несколько опций испытательного стенда, кодер генерирует один испытательный стенд и скрипт для каждого типа выбранного испытательного стенда. Если вы выбираете HDL code coverage, скрипты испытательного стенда включают покрытие кода для вашего сгенерированного HDL-кода. Для получения дополнительной информации о различных видах испытательных стендов, смотрите, Выбирают Test Bench for Generated HDL Code. После того, как вы выберете свои опции испытательного стенда, нажмите Apply.

На Шаге 3.2, Generate RTL Code and Testbench, выбирают Generate test bench. Нажмите Apply, и затем нажмите Run This Task. Кодер генерирует HDL-код для вашей подсистемы, и испытательные стенды и скрипты, которые вы выбрали на шаге 3.1.3.

Если вы выбрали Cosimulation model, то шаг 3.3, Verify with HDL Cosimulation, появляется в HDL Workflow Advisor. Этот шаг автоматически запускает сгенерированную cosimulation модель. Модель сравнивает результат HDL-кода, запускающегося в вашем симуляторе HDL с выходом вашей Подсистемы Simulink.

Если вы выбрали HDL test bench, кодер генерирует скрипт компиляции, subsystemname_tb_compile, и скрипт запуска, subsystemname_tb_simhdl_prj/hdlsrc/ папка и запуск эти команды:modelname

do symmetric_fir_compile.do do symmetric_fir_tb_compile.do do symmetric_fir_tb_sim.do

Если вы выбрали SystemVerilog DPI test bench, кодер генерирует файл скрипта, subsystemname_dpi_tbhdl_prj/hdlsrc/ папка и запуск эта команда:modelname

do symmetric_fir_dpi_tb.do

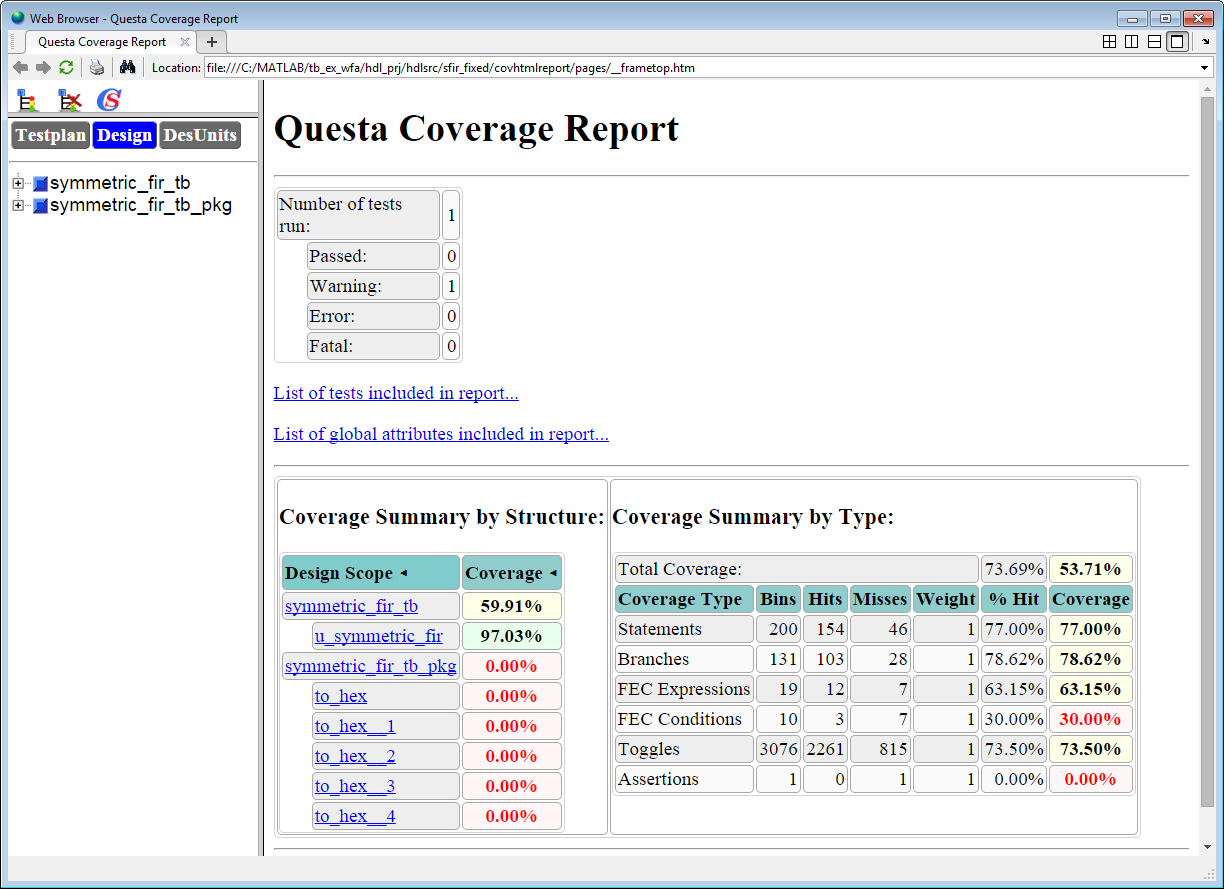

Если вы выбрали HDL code coverage, отчет покрытия кода от выполнения любого испытательного стенда, включая cosimulation модель, сохранен в hdl_prj\hdlsrc\.modelname\covhtmlreport