HDL Workflow Advisor предлагает рабочий процесс так, чтобы вы могли проверять вас алгоритм на совместимость HDL, генерировать HDL-код, проверять код, и затем развертывать код в вашу целевую платформу.

Можно запустить Советника по вопросам Рабочего процесса по алгоритму MATLAB® или модели Simulink®. Прежде чем вы развернете код в платформу целевого компьютера, установите инструмент синтеза и зададите путь к тому инструменту синтеза при помощи hdlsetuptoolpath функция. Смотрите Setup Инструмента.

Прежде чем вы зададите целевой рабочий процесс, когда вы запускаете Советника по вопросам Рабочего процесса из MATLAB, задаете проект и файлы испытательного стенда, задаете входные типы и запускаете преобразование фиксированной точки.

Задавать целевой рабочий процесс:

На панели инструментов MATLAB, от вкладки Apps, выбирают приложение HDL Coder.

Выберите проект MATLAB и файлы испытательного стенда и нажмите кнопку Workflow Advisor.

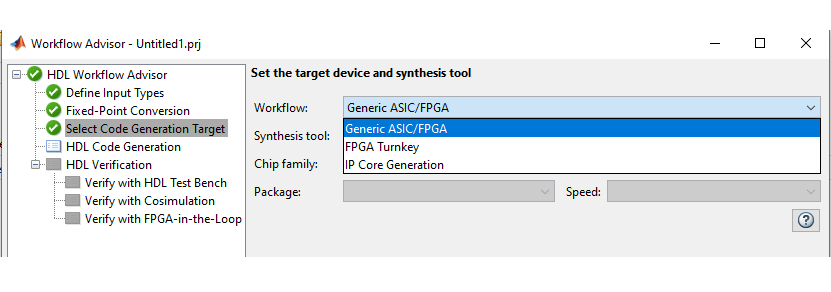

В Советнике по вопросам Рабочего процесса, на задаче Select Code Generation Target, выбирают Workflow.

Шаги после целевого изменения выбора генерации кода в зависимости от вашего целевого рабочего процесса.

Когда вы запускаете Советника по вопросам Рабочего процесса из своей модели Simulink, независимо от целевого рабочего процесса, вы запускаете шаги, чтобы подготовить модель к генерации HDL-кода, и затем сгенерировать код.

Откройте модель Simulink, для которой вы хотите запустить рабочий процесс.

На панели инструментов Simulink, от вкладки Apps, выбирают приложение HDL Coder.

На вкладке HDL Code нажмите кнопку Workflow Advisor.

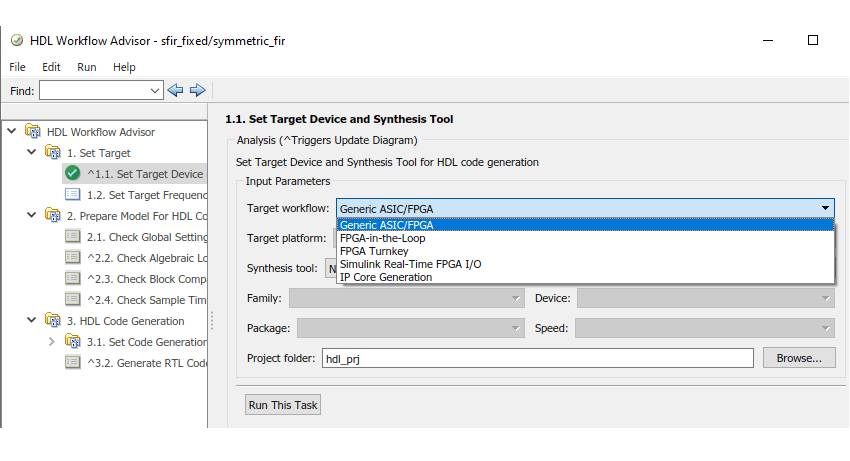

В HDL Workflow Advisor, на задаче Set Target Device and Synthesis Tool, выбирают Target workflow.

Шаги в Советнике по вопросам Рабочего процесса изменяются в зависимости от Target workflow, Target platform и Synthesis tool. Следующие разделы описывают больше о каждом из этих рабочих процессов.

Сгенерируйте HDL-код из своей модели Simulink или алгоритма MATLAB, проверьте HDL-код и разверните код в типовой ASIC или устройство FPGA. Можно выбрать из семейства устройств, которые принадлежат этим инструментам синтеза, как перечислено в Типовом Оборудовании ASIC/FPGA.

При помощи этого рабочего процесса вы можете:

Сгенерируйте HDL-код для своего алгоритма MATLAB фиксированной точки или своей совместимой с HDL модели Simulink.

Сгенерируйте испытательный стенд HDL, и cosimulation испытательный стенд (требует HDL Verifier™), и скрипты, чтобы создать и запустить код и испытательный стенд. Можно также сгенерировать испытательные стенды SystemVerilog DPI, и покрытие кода при выполнении HDL Workflow Advisor Simulink (требует HDL Verifier).

Выполните анализ синтеза и синхронизации FPGA и быстрое прототипирование ваш проект на типовых платформах FPGA посредством интеграции со сторонними инструментами синтеза.

Назад - аннотируют модель информацией о критическом пути и другой информацией, полученной во время синтеза, и оптимизируют ваш проект для области и скорости.

Примечание

Если вы выбираете Intel Quartus Pro или Microsemi Libero SoC как Synthesis tool, задача Annotate Model with Synthesis Result не доступна. Чтобы видеть критический путь, запустите рабочий процесс к синтезу и затем откройте отчеты синхронизации.

Чтобы узнать больше, см.:

Разверните свою модель Simulink или алгоритм MATLAB на автономные платы FPGA и платформы SoC. Чтобы использовать этот рабочий процесс, необходимо выбрать VHDL как Language. Можно выбрать из одного из этих инструментов синтеза, как перечислено в Оборудовании Тюремщика FPGA.

Используйте этот рабочий процесс для:

Выберите платы от менеджера Совета FPGA, которые являются Turnkey Enabled или создают ваши собственные платы для развертывания.

Сгенерируйте HDL-код для целого проекта FPGA, алгоритма DUT и высокоуровневого HDL-кода обертки FPGA. Можно также задать ограничения отображения контакта.

Выполните анализ синтеза и синхронизации FPGA и быстрое прототипирование ваш проект на FPGA и платформах SoC посредством интеграции со сторонними инструментами синтеза.

Для примера смотрите Начало работы с Рабочим процессом Тюремщика FPGA.

Сгенерируйте код RTL и пользовательское ядро IP HDL из вашей модели Simulink или алгоритма MATLAB. Прежде чем вы запустите рабочий процесс, разделите ваш проект на компоненты, которые работают на программном обеспечении и компонентах, которые работают на оборудовании. Смотрите Рабочий процесс Элемента кода аппаратного программного обеспечения для Платформ SoC.

Ядро IP является общим и допускающим повторное использование компонентом HDL, который состоит из файлов определения ядра IP, HDL-код, сгенерированный для вашего алгоритма, C заголовочный файл с таблицей адресов регистра и отчетом ядра IP. См.:

Можно выбрать из одного из этих инструментов синтеза, как перечислено в Оборудовании Генерации Ядра IP.

Используйте этот рабочий процесс для:

Сгенерируйте типовой независимый от платы Xilinx® или ядро Intel® HDL IP.

Интегрируйте ядро IP в исходный проект, чтобы предназначаться для автономных плат FPGA или платформ SoC с Xilinx интегратор Vivado® IP или Intel Qsys.

Свяжитесь со сгенерированным ядром IP HDL при помощи встроенного процессора ARM или из MATLAB при помощи HDL Verifier MATLAB как Ведущее устройство AXI. Смотрите Настроенный для MATLAB Ведущее устройство AXI (HDL Verifier).

Можно интегрировать ядро IP HDL в HDL Coder™, обеспеченный исходные проекты, такие как default system reference design или в исходный проект, который вы создали. Чтобы узнать больше, см.:

Сгенерируйте HDL-код из своей модели Simulink и разверните код на модули ввода-вывода FPGA Speedgoat. Этот рабочий процесс требует Xilinx Vivado и использует IP Core Generation инфраструктура рабочего процесса, как упомянуто во вводе-выводе FPGA Simulink Real-Time: Целевой компьютер Speedgoat.

Запускать Simulink Real-Time FPGA I/O рабочий процесс, установите Библиотеку Speedgoat и Пакеты Интегрирования HDL Coder Speedgoat. После того, как вы установите пакеты интегрирования, можно выбрать Target platform и затем запустить рабочий процесс к:

Сгенерируйте допускающее повторное использование и общее ядро IP.

Интегрируйте ядро IP в исходный проект Speedgoat.

Сгенерируйте FPGA, передают поток битов и загружают поток битов на целевой компьютер.

Сгенерируйте модель Simulink Real-Time™. Модель является интерфейсной моделью подсистемы, которая содержит блоки, чтобы программировать FPGA и связаться с платой во время выполнения в реальном времени.

Чтобы узнать больше, смотрите Рабочий процесс Генерации Ядра IP для Программируемых Simulink Модулей ввода-вывода Speedgoat.

Протестируйте свою модель Simulink или алгоритм MATLAB на целевом FPGA. Этот рабочий процесс требует HDL Verifier. Можно выбрать из одного из этих инструментов синтеза, как перечислено в FPGA в Оборудовании цикла.

Используйте этот рабочий процесс для:

Выберите платы от менеджера Совета FPGA, которые являются FIL Enabled или создают ваши собственные платы для верификации. Смотрите Индивидуальную настройку Совета FPGA.

Сгенерируйте HDL-код для своего алгоритма MATLAB фиксированной точки или своей совместимой с HDL модели Simulink.

Выполните реализацию FPGA и подключение к целевой плате FPGA с помощью Ethernet, JTAG или PCI Express для симуляции FIL.

Чтобы узнать больше, см.:

Симуляция FIL с HDL Workflow Advisor для Simulink (HDL Verifier)

Симуляция FIL с HDL Workflow Advisor для MATLAB (HDL Verifier)