Вычислить величину и фазовый угол комплексного сигнала - оптимизировано для генерации кода ЛПВП с использованием алгоритма CORDIC

Системная панель инструментов DSP Поддержка HDL/Математические функции

Блок оптимизированной ЛПВП с комплексным углом к величине вычисляет величину и фазовый угол комплексного сигнала и обеспечивает аппаратные управляющие сигналы. Для достижения эффективной реализации ЛПВП блок использует конвейерный алгоритм CORDIC.

Этот блок можно использовать для реализации таких операций, как atan2 в аппаратном обеспечении.

dataIn - Комплексный входной сигналКомплексный входной сигнал, заданный как скаляр, вектор столбца, представляющий выборки во времени, или вектор строки, представляющий каналы. Использование векторного ввода увеличивает пропускную способность при использовании большего количества аппаратных ресурсов. Блок реализует логику преобразования параллельно для каждого элемента вектора. Входной вектор может содержать до 64 элементов.

double и single типы данных поддерживаются для моделирования, но не для генерации кода HDL.

Типы данных: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | fixed point

validIn - Достоверность входных данныхBoolean скалярКогда validIn имеет значение trueблок захватывает данные из входного порта dataIn. Сигнал validIn применяется ко всем выборкам в векторном входном сигнале.

Типы данных: Boolean

Magnitude - Величина входного сигналаВеличина входного сигнала, возвращаемого как скаляр, вектор столбца, представляющий выборки во времени, или вектор строки, представляющий каналы. Размеры этого порта соответствуют размерам порта dataIn.

Чтобы включить этот порт, установите для параметра Output format значение Magnitude and Angle или Magnitude.

Типы данных: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | fixdt([],N,0)

Angle - Угол входного сигналаУгол входного сигнала, возвращаемый как скаляр, вектор столбца, представляющий выборки во времени, или вектор строки, представляющий каналы. Размеры этого порта соответствуют размерам порта dataIn.

Чтобы включить этот порт, установите для параметра Output format значение Magnitude and Angle или Angle.

Типы данных: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | fixdt([],N,0)

validOut - Достоверность выходных данныхBoolean скалярБлок устанавливает значение validOut для true с указанием всех допустимых данных, возвращаемых на выходных портах величины или угла. Сигнал validOut применяется ко всем выборкам в векторном выходном сигнале.

Типы данных: Boolean

Number of iterations source - Источник количества итерацийAuto (по умолчанию) | Property Чтобы задать количество итераций на входе WL − 1, выберите Auto. Если вход имеет тип данных double или singleколичество итераций по умолчанию равно 16.

Чтобы задать количество итераций с помощью параметра Число итераций (Number of iterations), выберите Property.

Number of iterations - Количество итераций CORDICЧисло итераций должно быть меньше или равно входному значению WL − 1. Задержка блока зависит от количества выполненных итераций. Сведения о задержке см. в разделе Задержка.

Чтобы включить этот параметр, задайте для параметра Количество итераций источника значение Property.

Output format - Формат выходного сигналаMagnitude and Angle (по умолчанию) | Magnitude | AngleИспользуйте этот параметр, чтобы указать, какие выходные порты включены.

Для включения выходных портов «Величина» и «Угол» выберите Magnitude and Angle (по умолчанию).

Чтобы включить выходной порт Magnitude и отключить выходной порт Angle, выберите Magnitude.

Чтобы включить выходной порт Angle и отключить выходной порт Magnitude, выберите Angle.

Angle format - Формат угла выводаNormalized (по умолчанию) | RadiansДля возврата выходного значения Angle в виде значения фиксированной точки, нормализующего углы в диапазоне [-1,1], выберите Normalized. Дополнительные сведения см. в разделе Нормализованный формат угла.

Для возврата выходного значения Angle в виде фиксированной точки в диапазоне [-δ, δ] выберите Radians. При использовании этого блока для реализации atan2 , установите для этого параметра значение Radians.

Scale output - Масштаб выходных данныхon (по умолчанию) | offВыберите этот параметр для умножения выходного сигнала Angle на коэффициент усиления CORDIC. Блок реализует этот коэффициент усиления, используя архитектуру shift-and-add для множителя. Эта реализация может увеличить длину критического пути в конструкции.

Примечание

Если вы очистите этот параметр и примените коэффициент усиления CORDIC в другом месте конструкции, то вы должны исключить член δ/4. Поскольку алгоритм квадрантного отображения заменяет первую итерацию CORDIC отображением входов в угловой диапазон [0, δ/4], начальное вращение не вносит член усиления. Коэффициент усиления является произведением cos(atan(2-n)), для n от 1 до числа итераций - 1.

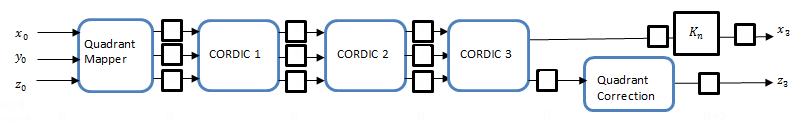

Алгоритм CORDIC является удобным для оборудования методом выполнения тригонометрических функций. Это итеративный алгоритм, который аппроксимирует решение, сходясь к идеальной точке. Блок использует режим векторизации CORDIC для итеративного поворота входных данных на действительную ось.

Метод Гивенса для поворота комплексного числа x + iy на угол Направление вращения, d, равно + 1 для против часовой стрелки и − 1 для по часовой.

Для аппаратной реализации, чтобы оставить член tan

Чтобы повернуть вектор на действительную ось, выберите ряд поворотов, таких, чтобы − n. Удалите член cosstart, чтобы в каждом итеративном повороте использовались только операции сдвига и добавления.

− 1 + dnxn − 12 − n

Объедините отсутствующие члены cosstartиз каждой итерации в константу и примените их с помощью одного множителя к результату конечного поворота. Выходная величина - это масштабированное конечное значение x. Выходной угол z - это сумма углов поворота.

RxNz=∑0Ndnθn

Область сходимости для стандартного вращения CORDIC равна ≈±99.7°. Чтобы обойти это ограничение, прежде чем выполнить какое-либо вращение, блок отображает входной сигнал в диапазон [0, δ/4] с помощью этого алгоритма.

if abs(x) > abs(y) input_mapped = [abs(x), abs(y)]; else input_mapped = [abs(y), abs(x)]; end

Квадрантное отображение экономит аппаратные ресурсы и уменьшает задержки, уменьшая количество этапов конвейера CORDIC на единицу. Коэффициент усиления CORDIC, Kn, поэтому не включает член n = 0 или cos (δ/4).

⋅cos (3,576)

После завершения итераций CORDIC блок корректирует угол обратно в исходное положение. Сначала он настраивает угол на правильную сторону δ/4.

if abs(x) > abs(y) angle_unmapped = CORDIC_out; else angle_unmapped = (pi/2) - CORDIC_out; end

if (x < 0)

if (y < 0)

output_angle = - pi + angle_unmapped;

else

output_angle = pi - angle_unmapped;

else

if (y<0)

output_angle = -angle_unmapped;

Блок генерирует конвейерную архитектуру ЛПВП для максимизации пропускной способности. Каждая итерация CORDIC выполняется в одном этапе трубопровода. Коэффициент усиления, если он включен, реализуется с помощью логики канонических цифр со знаком (CSD).

При использовании векторного ввода этот блок параллельно реплицирует эту архитектуру для каждого элемента вектора.

В следующей таблице показана длина выходного слова величины и угла (WL) для конкретной длины входного слова (WL). FL обозначает дробную длину, используемую в представлении с фиксированной точкой.

| Длина входного слова | Длина слова выходной величины |

|---|---|

| fixdt (0,WL,FL) | fixdt (0,WL + 2,FL) |

| fixdt (1,WL,FL) | fixdt (1,WL + 1,FL) |

| Длина входного слова | Длина слова угла вывода | |

|---|---|---|

| fixdt ([], WL, FL) | Радианы | fixdt (1,WL + 3,WL) |

| Нормализованный | fixdt (1, WL + 3, WL + 2) | |

Логика CORDIC на каждом этапе конвейера реализует одну итерацию. Для каждой ступени трубопровода сдвиг и угол поворота являются константами.

При установке для параметра «Формат вывода» значения Magnitudeблок не генерирует код ЛПВП для логики накопления угла и коррекции квадранта.

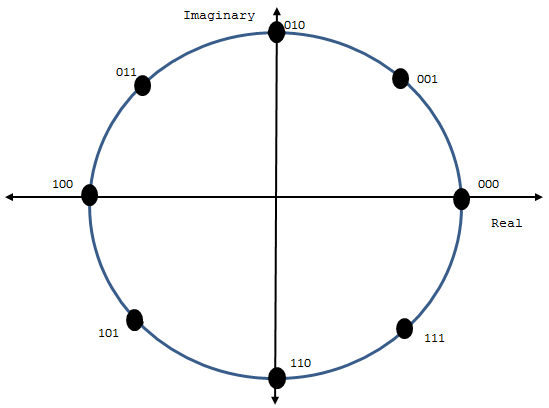

Этот формат нормализует значения радианного угла с фиксированной точкой вокруг единичной окружности. Это использование битов может быть более эффективным, чем использование диапазона [0, 2δ] радиан. Также этот нормализованный формат угла позволяет оборачивать угол при 0 или 2δ без дополнительного обнаружения и правильной логики.

Например, представление угла с 3 битами приводит к этим нормированным значениям.

Блок нормализует углы через [0, δ/4] и отображает их в правильный октант в конце вычисления.

Когда применяется допустимый ввод, допустимый вывод приходит после числа итераций + 4 цикла.

Если для параметра Источник числа итераций задано значение Property, блок показывает задержку немедленно. Если для параметра Число итераций (Number of iterations source) задано значение Autoблок вычисляет задержку на основе типа данных входного порта и отображает задержку при обновлении модели.

Если для параметра Источник числа итераций задано значение Auto, число итераций - входной WL − 1, а задержка - входной WL + 3. Если вход имеет тип данных double или singleчисло итераций равно 16, а задержка равна 20.

Производительность была измерена для конфигурации по умолчанию, с отключенным масштабированием выходных данных и fixdt(1,16,12) вход. Когда сгенерированный код HDL синтезируется в Xilinx ® Virtex ® -6 (XC6VLX240T-1FFG1156) FPGA, конструкция достигает тактовой частоты 260 МГц. Он использует следующие ресурсы.

| Ресурс | Используемый номер |

|---|---|

| LUT | 882 |

| FFS | 792 |

DSP48 Xilinx LogiCORE ® | 0 |

| Блок ОЗУ (16K) | 0 |

Производительность синтезированного HDL-кода зависит от цели и вариантов синтеза. При использовании векторного ввода использование ресурсов примерно равно VectorSize, умноженному на использование скалярных ресурсов.

Этот блок поддерживает генерацию кода C/C + + для режимов ускорения Simulink ® и быстрого ускорения, а также для генерации компонентов DPI.

HDL Coder™ предоставляет дополнительную опцию конфигурации, которая влияет на реализацию HDL и синтезированную логику.

Этот блок имеет единую архитектуру HDL по умолчанию.

| ConstrainedOutputPipeline | Количество регистров для размещения на выходах путем перемещения существующих задержек в рамках проекта. Распределенная конвейерная обработка не перераспределяет эти регистры. Значение по умолчанию: |

| InputPipeline | Количество входных ступеней трубопровода для вставки в сформированный код. Распределенная конвейерная обработка и конвейерная обработка с ограниченным выходом могут перемещать эти регистры. Значение по умолчанию: |

| OutputPipeline | Количество выходных ступеней трубопровода для вставки в сформированный код. Распределенная конвейерная обработка и конвейерная обработка с ограниченным выходом могут перемещать эти регистры. Значение по умолчанию: |

Этот блок поддерживает генерацию кода для сложных сигналов.

atan2 | dsp.HDLComplexToMagnitudeAngle | От комплекса до величины - угол (Симулинк)

1. Если смысл перевода понятен, то лучше оставьте как есть и не придирайтесь к словам, синонимам и тому подобному. О вкусах не спорим.

2. Не дополняйте перевод комментариями “от себя”. В исправлении не должно появляться дополнительных смыслов и комментариев, отсутствующих в оригинале. Такие правки не получится интегрировать в алгоритме автоматического перевода.

3. Сохраняйте структуру оригинального текста - например, не разбивайте одно предложение на два.

4. Не имеет смысла однотипное исправление перевода какого-то термина во всех предложениях. Исправляйте только в одном месте. Когда Вашу правку одобрят, это исправление будет алгоритмически распространено и на другие части документации.

5. По иным вопросам, например если надо исправить заблокированное для перевода слово, обратитесь к редакторам через форму технической поддержки.