Восходящий, фильтрующий и понижающий входной сигнал и генерирующий оптимизированный код HDL

Системная панель инструментов DSP Поддержка HDL/Фильтрация

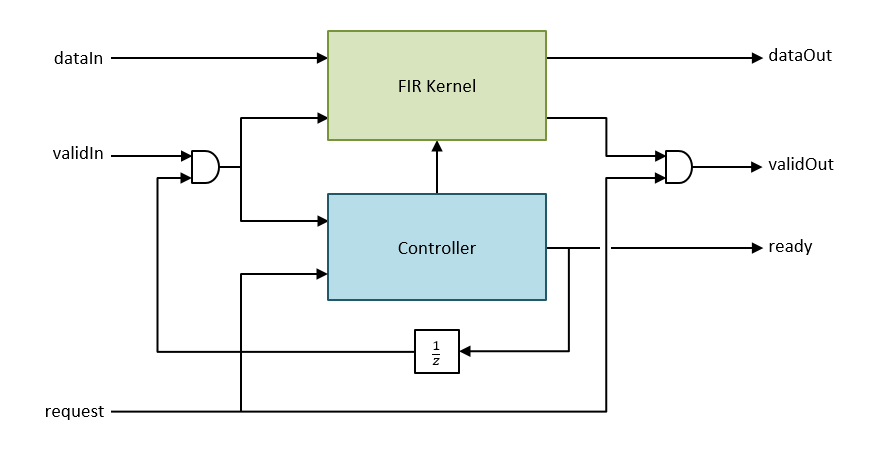

Блок HDL Optimized для преобразования КИХ (FIR Rate Conversion HDL Optimized) увеличивает пробы, фильтрует и понижает пробы входных сигналов. Он оптимизирован для генерации кода HDL и работает на одной выборке каждого канала одновременно. Блок реализует многофазную архитектуру, чтобы избежать ненужных арифметических операций и высоких промежуточных скоростей выборки.

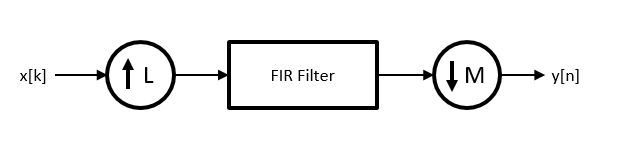

Блок увеличивает выборку входного сигнала на целочисленный коэффициент L, применяет его к КИХ-фильтру и понижает выборку входного сигнала на целочисленный коэффициент М.

Для отслеживания потока выборок можно использовать порты управления вводом и выводом. В конфигурации по умолчанию блок использует управляющие сигналы validIn и validOut. Для дополнительного управления потоком можно включить готовый выходной сигнал и входной сигнал запроса.

Выходной порт готовности указывает, что блок может принять новую выборку входных данных на следующем шаге времени. При L ≥ M можно использовать сигнал готовности для получения непрерывных выборок выходных данных. Если применить новый входной образец после каждого раза, блок возвращает готовый сигнал как 1, блок возвращает выборку выходных данных с сигналом validOut, установленным на 1 на каждом временном шаге.

При отключении порта ready можно применять допустимую выборку данных только каждый ceil(L/M) временные шаги. Например, если:

L/M = 4/5, затем можно применить новую входную выборку на каждом шаге времени.

L/M = 3/2, затем можно применить новую входную выборку на каждом другом шаге времени.

При включении входного порта запроса блок возвращает следующий выходной образец, когда сигнал запроса равен 1 и доступна действительная выходная выборка. При отключении порта запроса блок возвращает выходные выборки, когда они доступны. Если новые данные отсутствуют, блок устанавливает для сигнала validate Out значение 0.

Входной порт запроса можно подключить к готовому выходному порту дочернего блока.