Вычисляет обратное быстрое преобразование Фурье и генерирует оптимизированный код HDL

Системная панель инструментов DSP Поддержка HDL/Преобразования

Блок IFFT HDL Optimized предоставляет две архитектуры, реализующие алгоритм для приложений FPGA и ASIC. Можно выбрать архитектуру, которая оптимизирует пропускную способность или область.

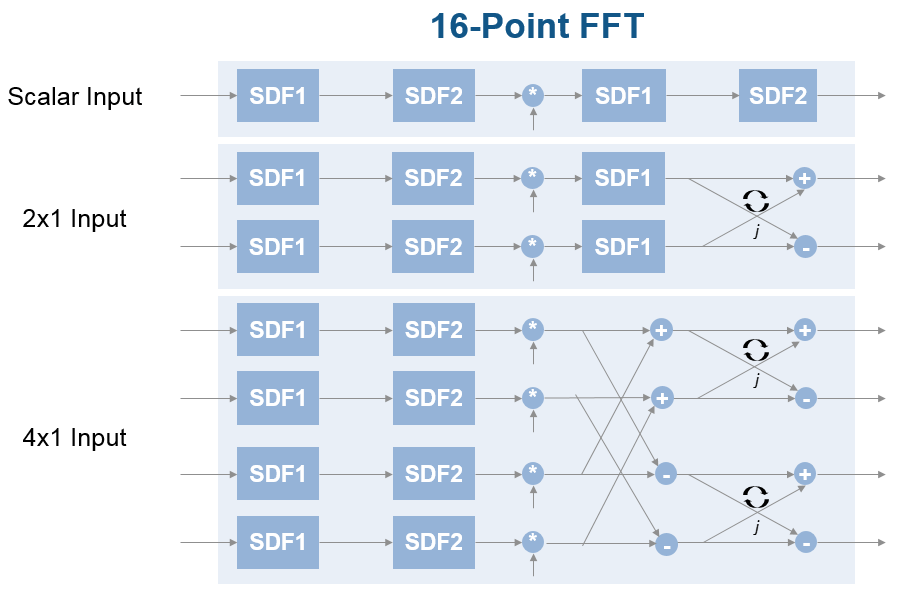

Streaming Radix 2^2 - Используйте эту архитектуру для высокопроизводительных приложений. Эта архитектура поддерживает скалярные или векторные входные данные. С помощью векторного ввода можно достичь пропускной способности giga-sample-per-second (GSPS).

Burst Radix 2 - Используйте эту архитектуру для минимальной реализации ресурсов, особенно с большими размерами быстрого преобразования Фурье (FFT). Система должна быть в состоянии выдерживать пакетные данные и более высокую задержку. Эта архитектура поддерживает только скалярные входные данные.

IFFT HDL Optimized принимает реальные или сложные данные, обеспечивает аппаратные управляющие сигналы и дополнительные выходные сигналы управления кадрами.

data - Входные данныеВходные данные, определяемые как скалярный или столбчатый вектор вещественных или комплексных значений. Только Streaming Radix 2^2 архитектура поддерживает векторный ввод. Размер вектора должен быть степенью 2 в диапазоне от 1 до 64 и меньше или равен длине БПФ.

double и single типы данных поддерживаются для моделирования, но не для генерации кода HDL.

Типы данных: int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | fixed point | single | double

Поддержка комплексного номера: Да

valid - Указывает допустимые входные данныеЭтот порт указывает, являются ли входные данные допустимыми. При допустимом вводе: true (1), блок фиксирует значение на входном порте данных. При допустимом вводе: false (0), блок игнорирует выборки входных данных.

Типы данных: Boolean

reset - Сигнал управления сбросомПри сбросе true (1), блок останавливает текущий расчет и очищает все внутренние состояния. Блок запускает новый кадр, когда выполняется сброс false (0) и действительным входным значением является true (1).

Чтобы включить этот порт, выберите параметр Enable reset input port.

Типы данных: Boolean

data - Выходные данные частотного каналаЕсли для ввода используется тип данных с фиксированной точкой и включено масштабирование, тип выходных данных совпадает с типом входных данных. Если вход имеет целочисленный тип, а масштабирование включено, то на выходе используется тип с фиксированной точкой с той же длиной слова, что и на входе. Порядок вывода по умолчанию изменяется на битовый. Если масштабирование отключено, длина выходного слова увеличивается во избежание переполнения. Только Streaming Radix 2^2 архитектура поддерживает векторный ввод и вывод. Дополнительные сведения см. в разделе Разделение выходов бабочек на два параметра.

Типы данных: fixed point | double | single

Поддержка комплексного номера: Да

valid - Указывает допустимые выходные данные Этот порт указывает, что выходные данные являются допустимыми. Когда допустимо true (1), блок возвращает действительные данные на выходном порте данных. Когда допустимо false (0), недопустимые значения порта выходных данных.

Типы данных: Boolean

ready - Указывает, что блок готовЭтот порт указывает, что блок готов для нового входного образца. Когда готов true (1), блок принимает входные данные на следующем временном шаге, и когда готов false (0), блок игнорирует входные данные на следующем шаге времени.

Порт появляется в блоке при установке для параметра Architecture значения Burst Radix 2.

Типы данных: Boolean

start - Указывает первый допустимый цикл выходных данныхПри включении этого порта блок устанавливает начальный выход на true (1) во время первого действительного цикла кадра выходных данных.

Чтобы включить этот порт, выберите параметр Enable start output port.

Типы данных: Boolean

end - Указывает последний допустимый цикл выходных данныхПри включении этого порта блок устанавливает конечный выход на true (1) во время последнего допустимого цикла кадра выходных данных.

Чтобы включить этот порт, выберите параметр Enable end output port.

Типы данных: Boolean

FFT length - Количество точек данных, используемых для одного расчета БПФ1024 (по умолчанию)Этот параметр определяет количество точек данных, используемых для одного вычисления обратного быстрого преобразования Фурье (IFFT). Для генерации кода HDL длина БПФ должна быть мощностью 2 между 23 и 216.

Architecture - Тип архитектурыStreaming Radix 2^2 (по умолчанию) | Burst Radix 2Этот параметр определяет тип архитектуры.

Streaming Radix 2^2 - Выберите это значение, чтобы указать архитектуру с низкой задержкой. Этот тип архитектуры поддерживает пропускную способность GSPS при использовании векторного ввода.

Burst Radix 2 - Выберите это значение, чтобы указать минимальную архитектуру ресурсов. Этот тип архитектуры не поддерживает векторный ввод.

Для генерации кода HDL длина БПФ должна быть мощностью 2 между 23 и 216.

Дополнительные сведения об этих архитектурах см. в разделе Алгоритмы.

Complex Multiplication - внедрение ЛПВПUse 4 multipliers and 2 adders (по умолчанию) | Use 3 multipliers and 5 addersЭтот параметр определяет тип комплексного множителя для реализации HDL. Каждое умножение реализуется либо с Use 4 multipliers and 2 adders или с Use 3 multipliers and 5 adders. Скорость реализации зависит от используемого средства синтеза и целевого устройства.

Output in bit-reversed order - Порядок выходных данныхЭтот параметр возвращает выходные элементы в битовом порядке.

При выборе этого параметра выходные элементы преобразуются в биты. Чтобы вернуть выходные элементы в линейном порядке, очистите этот параметр.

Алгоритм IFFT вычисляет выход в обратном порядке к входу. Если вы указываете выход в том же порядке, что и вход, алгоритм выполняет дополнительную операцию реверсирования. Дополнительные сведения см. в разделе Линейный и реверсированный порядок вывода.

Input in bit-reversed order - Ожидаемый порядок входных данныхПри выборе этого параметра блок ожидает входные данные в обратном порядке. По умолчанию флажок снят, и ввод ожидается в линейном порядке.

Алгоритм IFFT вычисляет выход в обратном порядке к входу. Если вы указываете выход в том же порядке, что и вход, алгоритм выполняет дополнительную операцию реверсирования. Дополнительные сведения см. в разделе Линейный и реверсированный порядок вывода.

Divide butterfly outputs by two - Масштабирование БПФПри выборе этого параметра блок реализует общий масштабный коэффициент 1/N путем деления выходного сигнала каждого умножения бабочек на два. Эта регулировка поддерживает выход IFFT в том же диапазоне амплитуд, что и его вход. При отключении масштабирования блок избегает переполнения, увеличивая длину слова на 1 бит после каждого умножения бабочки. Увеличение битов одинаково для обеих архитектур.

Rounding Method - Режим округления для внутренних расчетов с фиксированной точкойFloor (по умолчанию) | Ceiling | Convergent | Nearest | Round | ZeroЭтот параметр позволяет выбрать тип режима округления для внутренних вычислений с фиксированной точкой. Дополнительные сведения о режимах округления см. в разделе Метод округления. Если входным значением является целое число или тип данных с фиксированной точкой, алгоритм IFFT использует арифметику с фиксированной точкой для внутренних вычислений. Этот параметр не применяется при вводе single или double тип. Округление применяется к операциям умножения и масштабирования сдвоенного коэффициента.

Enable reset input port - Дополнительный сигнал сбросаЭтот параметр включает входной порт сброса. При выборе этого параметра на значке блока появляется входной порт сброса.

Enable start output port - Дополнительный управляющий сигнал, указывающий на начало данныхЭтот параметр активизирует порт, указывающий начало выходных данных. При выборе этого параметра на значке блока появляется выходной начальный порт.

Enable end output port - Дополнительный управляющий сигнал, указывающий на конец данныхЭтот параметр активизирует порт, указывающий конец выходных данных. При выборе этого параметра на значке блока появляется выходной конечный порт.

Потоковая архитектура Radix 2 ^ 2 реализует архитектуру с низкой задержкой. Это экономит ресурсы по сравнению с потоковой реализацией Radix 2 за счет факторинга и группирования уравнения FFT. Архитектура имеет этапы log4 (N). Каждая ступень содержит две кнопки обратной связи с однопутевой задержкой (SDF) с контроллерами памяти. При использовании векторного ввода каждый этап работает на меньшем количестве входных выборок, поэтому некоторые этапы сводятся к простой бабочке, без SDF.

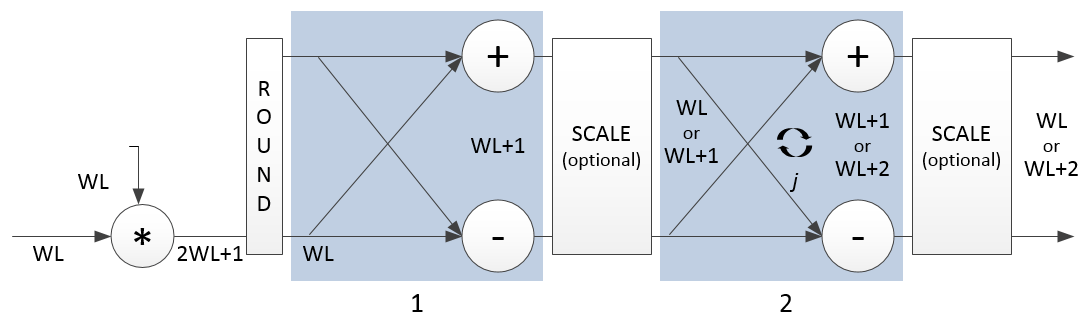

Первая ступень SDF - обычная бабочка. Второй каскад умножает выходы первого каскада на -j. Чтобы избежать аппаратного множителя, блок заменяет действительную и мнимую части входов и снова заменяет мнимые части результирующих выходов. Каждый этап округляет результат умножения множителя до длины входного слова. Сдвоенные коэффициенты имеют два целых бита, а остальные биты используются для дробных битов. Сдвоенные коэффициенты имеют такую же битовую ширину, как и входные данные WL. Множители twiddle имеют два целых бита и WL-2 дробные биты.

При включении масштабирования алгоритм делит результат каждого этапа бабочки на 2. Масштабирование на каждом этапе позволяет избежать переполнения, сохранить длину слова на уровне входных данных и получить общий масштабный коэффициент 1/N. Если масштабирование отключено, алгоритм избегает переполнения, увеличивая длину слова на 1 бит на каждом этапе. На диаграмме показаны бабочки и внутренние длины слов каждого этапа, не включая память.

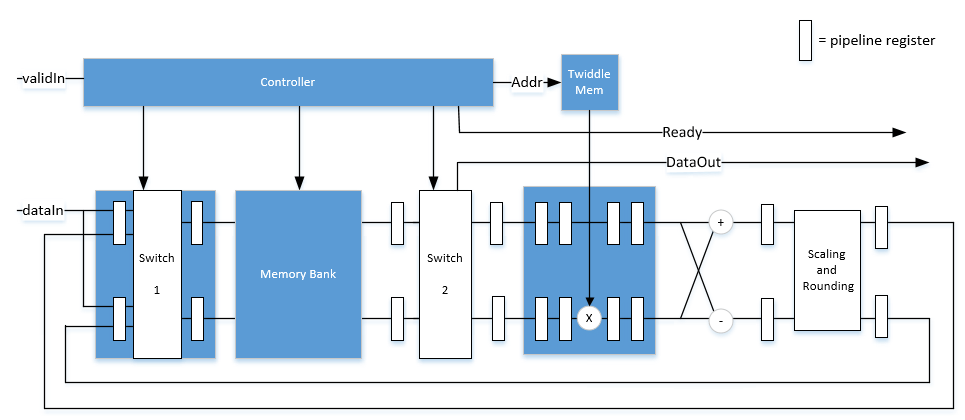

Пакетная архитектура Radix 2 реализует FFT с использованием единого комплексного умножителя бабочек. Алгоритм не может запуститься, пока не сохранит весь входной кадр, и не сможет принять следующий кадр до завершения вычислений. Выходной порт готовности указывает, когда алгоритм готов к новым данным. На схеме показана архитектура пакета с конвейерными регистрами.

Алгоритм обрабатывает входные данные только в том случае, если входной допустимый порт равен 1. Выходные данные действительны, только если выходной допустимый порт равен 1.

Если дополнительный входной порт сброса равен 1, алгоритм останавливает текущее вычисление и сбрасывает все внутренние состояния. Алгоритм начинает новые вычисления, когда порт сброса равен 0, а входной допустимый порт запускает новый кадр.

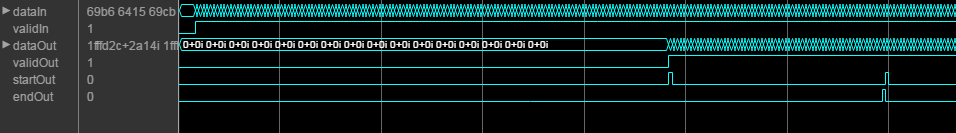

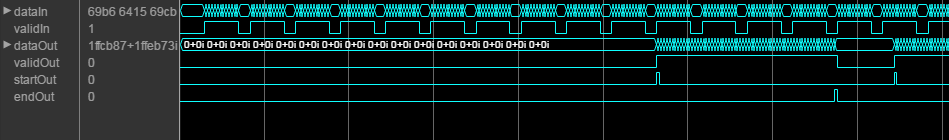

Эта диаграмма показывает входные и выходные допустимые значения портов для смежных скалярных входных данных, потоковой архитектуры Radix 2 ^ 2, длины FFT 1024 и размера вектора 16.

На схеме также показаны необязательные значения начального и конечного портов, указывающие границы кадра. Если начальный порт включен, значение начального порта будет импульсным в течение одного цикла с первым допустимым выходом кадра. Если конечный порт включен, значение начального порта будет импульсным в течение одного цикла с последним допустимым выходом кадра.

При применении непрерывных входных кадров выходные данные также будут непрерывными после начальной задержки.

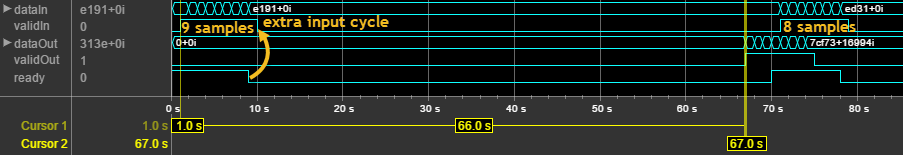

Входной допустимый порт может быть несмежным. Данные, сопровождаемые входным допустимым портом, обрабатываются по мере их поступления, и полученные данные сохраняются до тех пор, пока не будет заполнен кадр. Затем алгоритм возвращает непрерывные выходные выборки в кадре из N циклов (длины БПФ). Эта диаграмма показывает несмежный вход и смежный выход для длины БПФ 512 и размера вектора 16.

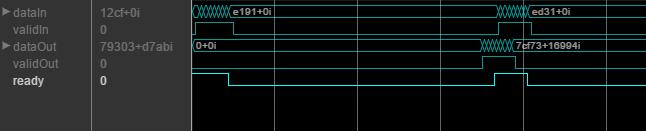

При использовании архитектуры пакета невозможно предоставить следующий кадр входных данных до тех пор, пока не будет доступно пространство памяти. Порт готовности указывает, когда алгоритм может принимать новые входные данные.

Задержка зависит от длины БПФ и размера входного вектора. После обновления модели значок блока отображает задержку. Отображаемая задержка - это количество циклов между первым действительным входом и первым действительным выходом, при условии, что вход является непрерывным. Чтобы получить эту задержку программным способом, см. раздел Автоматическое согласование задержки блока, оптимизированного для БПФ HDL.

При использовании пакетной архитектуры с непрерывным входом, если проект ожидает готовности к выходу 0 перед отменой действительности ввода на вход поступает один дополнительный цикл данных. Этот образец данных является первым образцом следующего кадра. Алгоритм может сохранить один образец при обработке текущего кадра. Благодаря этому опережению одной выборки наблюдаемая задержка более поздних кадров (от действительного входного до действительного выходного) на один цикл короче, чем сообщаемая задержка. Задержка измеряется от первого цикла, когда действительность ввода равна 1, до первого цикла, когда действительность вывода равна 1. Число циклов между, когда порт готовности равен 0, а выходной допустимый порт равен 1, всегда является задержкой - FFTLength.

Эти данные о ресурсах и производительности являются результатом синтеза генерируемого HDL, предназначенного для Xilinx ® Virtex ® -6 (XC6VLX75T-1FF484) FPGA. Примеры в таблицах имеют следующую конфигурацию:

1024 Длина БПФ (по умолчанию)

Комплексное умножение с использованием 4 умножителей, 2 сумматоров

Масштабирование выходных данных включено

Вход естественного порядка, выход с реверсированием битов

16-разрядные комплексные входные данные

Включение синхронизации минимизировано (параметр HDL Coder™)

Производительность синтезированного HDL-кода зависит от цели и вариантов синтеза. Например, при переупорядочивании для выхода естественного порядка используется больше ОЗУ, чем для выхода с обращенным разрядом по умолчанию, а при реальном вводе используется меньше ОЗУ, чем при сложном входе.

Для скалярной входной конфигурации Radix 2 ^ 2 конструкция достигает тактовой частоты 326 МГц. Задержка составляет 1116 циклов. Эти ресурсы используются в проекте.

| Ресурс | Используемый номер |

|---|---|

| LUT | 4597 |

| FFS | 5353 |

DSP48 Xilinx LogiCORE ® | 12 |

| Блок ОЗУ (16K) | 6 |

При векторизации одной и той же реализации Radix 2 ^ 2 для параллельной обработки двух 16-битных входных выборок конструкция достигает тактовой частоты 316 МГц. Задержка составляет 600 циклов. Эти ресурсы используются в проекте.

| Ресурс | Используемый номер |

|---|---|

| LUT | 7653 |

| FFS | 9322 |

DSP48 Xilinx LogiCORE | 24 |

| Блок ОЗУ (16K) | 8 |

Блок поддерживает скалярные входные данные только при реализации пакетной архитектуры Radix 2. Конструкция пакета достигает тактовой частоты 309 МГц. Задержка составляет 5811 циклов. Эти ресурсы используются в проекте.

| Ресурс | Используемый номер |

|---|---|

| LUT | 971 |

| FFS | 1254 |

DSP48 Xilinx LogiCORE | 3 |

| Блок ОЗУ (16K) | 6 |

Этот блок поддерживает генерацию кода C/C + + для режимов ускорения Simulink ® и быстрого ускорения, а также для генерации компонентов DPI.

Кодер HDL предоставляет дополнительные опции конфигурации, которые влияют на реализацию HDL и синтезированную логику.

Этот блок имеет единую архитектуру HDL по умолчанию.

| ConstrainedOutputPipeline | Количество регистров для размещения на выходах путем перемещения существующих задержек в рамках проекта. Распределенная конвейерная обработка не перераспределяет эти регистры. Значение по умолчанию: |

| InputPipeline | Количество входных ступеней трубопровода для вставки в сформированный код. Распределенная конвейерная обработка и конвейерная обработка с ограниченным выходом могут перемещать эти регистры. Значение по умолчанию: |

| OutputPipeline | Количество выходных ступеней трубопровода для вставки в сформированный код. Распределенная конвейерная обработка и конвейерная обработка с ограниченным выходом могут перемещать эти регистры. Значение по умолчанию: |

При использовании блока IFFT HDL Optimized с блоком управления состоянием (HDL Coder) внутри включенной подсистемы (Simulink) дополнительный порт сброса не поддерживается. Если включить порт сброса в блоке IFFT HDL Optimized в такой подсистеме, то при обновлении схемы в модели возникнет ошибка.

1. Если смысл перевода понятен, то лучше оставьте как есть и не придирайтесь к словам, синонимам и тому подобному. О вкусах не спорим.

2. Не дополняйте перевод комментариями “от себя”. В исправлении не должно появляться дополнительных смыслов и комментариев, отсутствующих в оригинале. Такие правки не получится интегрировать в алгоритме автоматического перевода.

3. Сохраняйте структуру оригинального текста - например, не разбивайте одно предложение на два.

4. Не имеет смысла однотипное исправление перевода какого-то термина во всех предложениях. Исправляйте только в одном месте. Когда Вашу правку одобрят, это исправление будет алгоритмически распространено и на другие части документации.

5. По иным вопросам, например если надо исправить заблокированное для перевода слово, обратитесь к редакторам через форму технической поддержки.