Подсистема, выполнение которой включено внешним входом

Simulink/Порты и подсистемы

Кодер HDL/Порты и подсистемы

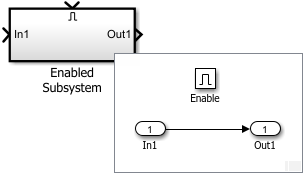

Блок Enabled Subsystem - это блок Subsystem, предварительно сконфигурированный как начальная точка для создания подсистемы, которая выполняется, когда управляющий сигнал имеет положительное значение.

Использование блоков включенной подсистемы для моделирования:

Неоднородности

Дополнительная функциональность

Альтернативная функциональность

In - Вход сигнала в блок подсистемыВход сигнала в блок подсистемы, заданный как скаляр, вектор или матрица. При размещении блока Inport в блоке Subsystem к блоку добавляется внешний входной порт. Метка порта соответствует имени блока Inport.

Блоки Inport используются для приема сигналов из локальной среды.

Типы данных: half | single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | Boolean | fixed point | enumerated | bus

Enable - Вход управляющего сигнала в блок подсистемыБлок Enable в блоке Subsystem добавляет внешний входной порт к блоку и делает его блоком Enabled Subsystem.

Типы данных: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | Boolean | fixed point

Out - Выход сигнала из блока подсистемыВыходной сигнал блока подсистемы, возвращаемый в виде скаляра, вектора или матрицы. При размещении блока Outport в блоке Subsystem к блоку добавляется внешний выходной порт. Метка порта соответствует имени блока Outport.

Блоки Outport используются для передачи сигналов в локальную среду.

Типы данных: half | single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | Boolean | fixed point | enumerated | bus

Типы данных |

|

Прямой проход |

|

Многомерные сигналы |

|

Сигналы переменного размера |

|

Обнаружение пересечения нулей |

|

[a] Фактический тип данных или поддержка возможностей зависит от реализации блока. | |

Фактическая поддержка генерации кода зависит от реализации блока.

HDL Coder™ предоставляет дополнительные опции конфигурации, которые влияют на реализацию HDL и синтезированную логику.

При использовании включенных подсистем в моделях, предназначенных для генерации кода HDL, рекомендуется учитывать следующее:

Чтобы результаты синтеза соответствовали результатам Simulink ®, порт Enable должен управляться зарегистрированной логикой (с синхронным синхросигналом) на FPGA.

Установите задержки блока на выходные сигналы включенной подсистемы. Это предотвращает вставку генератором кода дополнительных байпасных регистров в код HDL.

Включенные подсистемы могут влиять на результаты синтеза следующими способами:

В некоторых случаях тактовая частота системы может снизиться на небольшой процент.

Созданный код использует больше ресурсов, масштабирование с количеством включенных экземпляров подсистемы и количеством выходных портов на подсистему.

| Архитектура | Описание |

|---|---|

Module (по умолчанию) | Создайте код для подсистемы и блоков в подсистеме. |

BlackBox | Создайте интерфейс черного ящика. Сгенерированный код HDL включает только определения портов ввода/вывода для подсистемы. Поэтому можно использовать подсистему в модели для создания интерфейса с существующим, написанным вручную кодом HDL. Генерация интерфейса черного ящика для подсистем аналогична генерации интерфейса блока модели без тактовых сигналов. |

| Удалите подсистему из сгенерированного кода. При моделировании можно использовать подсистему, однако в коде HDL ее можно рассматривать как «no-op». |

| Общая информация | |

|---|---|

| AdaptivePipelining | Автоматическая вставка трубопровода на основе инструмента синтеза, целевой частоты и длины слова множителя. Значение по умолчанию: |

| BalanceDelays | Обнаруживает введение новых задержек по одному пути и вставляет совпадающие задержки по другим путям. Значение по умолчанию: |

| ClockRatePipelining | Вставка регистров конвейера с более высокой тактовой частотой вместо более низкой скорости передачи данных. Значение по умолчанию: |

| ConstrainedOutputPipeline | Количество регистров для размещения на выходах путем перемещения существующих задержек в рамках проекта. Распределенная конвейерная обработка не перераспределяет эти регистры. Значение по умолчанию: |

| DistributedPipelining | Распределение регистров трубопроводов или ресинхронизация регистров. Значение по умолчанию: |

| DSPStyle | Атрибуты синтеза для отображения множителя. Значение по умолчанию: |

| FlattenHierarchy | Удалите иерархию подсистемы из сгенерированного кода HDL. Значение по умолчанию: |

| InputPipeline | Количество входных ступеней трубопровода для вставки в сформированный код. Распределенная конвейерная обработка и конвейерная обработка с ограниченным выходом могут перемещать эти регистры. Значение по умолчанию: |

| OutputPipeline | Количество выходных ступеней трубопровода для вставки в сформированный код. Распределенная конвейерная обработка и конвейерная обработка с ограниченным выходом могут перемещать эти регистры. Значение по умолчанию: |

| SharingFactor | Количество функционально эквивалентных ресурсов для сопоставления с одним общим ресурсом. Значение по умолчанию - 0. См. также раздел Совместное использование ресурсов (кодер HDL). |

| StreamingFactor | Количество параллельных путей данных, или векторов, которые мультиплексируются по времени для преобразования в последовательные скалярные пути данных. По умолчанию используется значение 0, которое реализует полностью параллельные пути данных. См. также Потоковая передача (кодер HDL). |

Целевая спецификация

Этот блок не может быть DUT, поэтому параметры свойств блока на вкладке «Целевая спецификация» игнорируются.

Кодер HDL поддерживает генерацию кода HDL для включенных подсистем, удовлетворяющих следующим условиям:

Включенная подсистема не является DUT.

Подсистема не активирована и не активирована.

Сигнал разрешения является скалярным.

Выходы включенной подсистемы имеют начальное значение 0.

Все входы и выходы включенной подсистемы (включая разрешающий сигнал) работают с одинаковой скоростью.

Параметр Show output port блока Enable имеет значение Off.

Состояние, когда параметр enabling блока Enable имеет значение held (т.е. блок Enable не сбрасывает состояния, когда он включен).

Параметр Output when disabled для включенных портов вывода подсистемы имеет значение held (т.е. включенная подсистема не сбрасывает выходные значения при отключении).

Если DUT содержит следующие блоки, RAMArchitecture имеет значение WithClockEnable:

Двухпортовая ОЗУ

Простая двухпортовая оперативная память

Однопортовая ОЗУ

Включенная подсистема не содержит следующих блоков:

Децимация CIC

Интерполяция CIC

Децимация РПИ

Интерполяция FIR

Субдискретизировать

Сверхдискретизировать

HDL FIFO

Блоки косимуляции ЛПВП (Verifier™ ЛПВП)

Переход ставки

Полярный кодер NR и полярный декодер NR (беспроводной HDL Toolbox™)

Пример автоматического контроллера усиления показывает, как можно использовать включенные подсистемы при создании кода HDL. Для открытия примера введите:

hdlcoder_agc

Фактическая поддержка типа данных зависит от реализации блока.

1. Если смысл перевода понятен, то лучше оставьте как есть и не придирайтесь к словам, синонимам и тому подобному. О вкусах не спорим.

2. Не дополняйте перевод комментариями “от себя”. В исправлении не должно появляться дополнительных смыслов и комментариев, отсутствующих в оригинале. Такие правки не получится интегрировать в алгоритме автоматического перевода.

3. Сохраняйте структуру оригинального текста - например, не разбивайте одно предложение на два.

4. Не имеет смысла однотипное исправление перевода какого-то термина во всех предложениях. Исправляйте только в одном месте. Когда Вашу правку одобрят, это исправление будет алгоритмически распространено и на другие части документации.

5. По иным вопросам, например если надо исправить заблокированное для перевода слово, обратитесь к редакторам через форму технической поддержки.