Определенные схемы или комбинация блоков с регистрами могут улучшить достижимую тактовую частоту и уменьшить использование области на платах FPGA. Адаптивная оптимизация конвейеров создает эти массивы путем вставки регистров трубопроводов в блоки в проекте. Чтобы определить оптимальное количество регистров трубопровода для вставки в конструкцию, оптимизация учитывает целевое устройство, целевую частоту, длину слова умножителя и настройки в свойствах блока HDL. Используйте адаптивную конвейерную обработку с:

Конвейер тактовой частоты для вставки регистров конвейера с более высокой тактовой частотой вместо более низкой скорости передачи данных. С помощью конвейера тактовой частоты можно разработать DUT с одной скоростью, а затем указать коэффициент избыточной дискретизации.

Совместное использование ресурсов экономит область и время, поскольку генератор кода совместно использует ресурсы и вставляет адаптивные регистры конвейера.

По умолчанию в модели отключена оптимизация адаптивной конвейерной обработки. В определенных ситуациях перед созданием кода HDL необходимо включить эту оптимизацию. См. раздел Образцы конструкции, требующие адаптивной конвейерной обработки.

Для Coder™ HDL для вставки адаптивных трубопроводов укажите целевое устройство. При наличии множителей укажите целевое устройство и целевую частоту.

Примечание

Если вы используете целевое устройство, которое не характеризуется для адаптивной конвейеризации, оптимизация использует Xilinx ® Virtex ® -7, когдаXilinx Vivado указывается как Synthesis Tool и использует Intel ® Stratix ® V, когда Synthesis Tool являетсяAltera Quartus II или Intel Quartus Pro.

Убедитесь, что для подсистемы, для которой требуется вставить адаптивные трубопроводы, включена балансировка задержки. При отключении балансировки задержки генератор кода не вставляет адаптивные трубопроводы.

Убедитесь, что в конструкции нет типов данных или операций с плавающей запятой.

Примечание

В некоторых случаях при наличии блоков внутри контура обратной связи адаптивная конвейерная обработка не может вставить необходимое количество регистров трубопровода на выходе. После этого может произойти сбой балансировки задержки.

Можно задать адаптивную конвейерную обработку для всей модели или для более точного управления можно задать адаптивную конвейерную обработку для подсистем в подсистеме DUT верхнего уровня.

По умолчанию адаптивная конвейерная обработка отключена на уровне модели. Можно включить адаптивную конвейерную обработку одним из следующих способов.

На вкладке «Создание кода HDL» > «Настройка параметров создания кода» > «Настройка параметров оптимизации» > «Конвейерная обработка» помощника по рабочим процессам HDL выберите «Адаптивная конвейерная обработка».

В диалоговом окне «Параметры конфигурации» на вкладке «Создание кода HDL» > «Оптимизация» > «Конвейерная обработка» выберите «Адаптивная конвейерная обработка» и нажмите «ОК».

В командной строке используйте команду makehdl или hdlset_param для установки адаптивного конвейерирования в значение on.

hdlset_param(gcs, 'AdaptivePipelining', 'on')

По умолчанию подсистемы модели наследуют настройку адаптивной конвейеризации на уровне модели. Если вы хотите, чтобы кодер HDL выборочно включил адаптивные трубопроводы для подсистемы в вашей модели, установите параметр Pipelining равным on для этой подсистемы.

Сведения о настройке адаптивной конвейерной обработки для подсистемы см. в разделе Настройка адаптивной конвейерной обработки для подсистемы.

Адаптивная конвейерная обработка поддерживает эти таблицы поиска, множители, блоки умножения и изменения скорости для автоматической вставки трубопровода.

n-D таблица подстановки

Таблица прямого поиска (n-D)

Оптимизированный Sine HDL

Оптимизация косинусного HDL

Субдискретизировать

Переход ставки

Продукт

Выгода

Умножение-сложение

Умножить - накапливать

Функция MATLAB

Чтобы вставить адаптивные трубопроводы для блоков Rate Transition и Downsample, выполните следующие действия.

Укажите целевое устройство.

Убедитесь, что для блоков Downsample коэффициент Downsample больше двух.

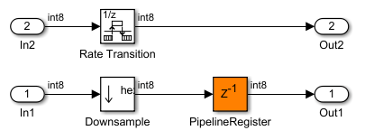

При генерации кода кодер HDL вставляет регистр трубопровода в выходной порт блока Downsample. Добавление регистра трубопровода может избежать логики байпасного регистра, что экономит область на целевом FPGA.

На этом рисунке представлена сгенерированная модель для блоков с Virtex7 Xilinx в качестве целевого устройства FPGA.

Для вставки адаптивных трубопроводов для этих блоков:

Укажите целевое устройство.

Укажите целевую частоту больше нуля.

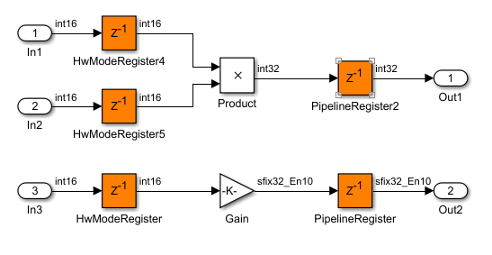

При формировании кода кодер HDL вставляет регистры на входном и выходном портах блоков. Комбинация множителей с регистрами может потенциально отображаться на блоки DSP на целевом устройстве.

На этом рисунке представлена модель для блоков Product, Gain и Multiply-Add с Intel Arria10 в качестве целевого устройства FPGA и целевой частотой 500 МГц. Входы в блоки имеют тип int16.

Шаблон и количество регистров конвейера, которые вставляет кодер HDL, могут изменяться в зависимости от целевого устройства, целевой частоты и длины слова умножителя.

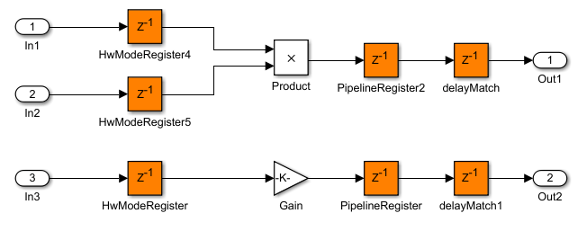

Этот рисунок представляет собой сгенерированную модель для блоков с Virtex7 Xilinx в качестве целевого устройства FPGA и целевой частотой 1500 МГц. Входные данные имеют тип int8.

Блоки имеют различное количество регистров конвейера на выходных портах. Чтобы согласовать задержки, кодер HDL добавляет задержку на выходе блоков Product и Gain.

Для вставки адаптивных трубопроводов для этих блоков:

Укажите целевое устройство.

Укажите целевую частоту больше нуля.

Используйте Parallel Архитектура HDL для блока Multiply-Accumulate. Для входного вектора размера N, эта архитектура использует N

Умножение (Multiply): добавление блоков последовательно для вычисления результата.

Внимание

Блок Multiply-Add с параметром PipelineDepth, равным auto или значение больше нуля и блок Multiply-Accumulate с архитектурой HDL, указанной как Parallel игнорировать параметр адаптивной конвейеризации. Если указать целевое устройство FPGA и целевую частоту больше нуля, генератор кода вставляет регистры конвейера на входы и выходы блока, даже если адаптивная конвейерная обработка отключена.

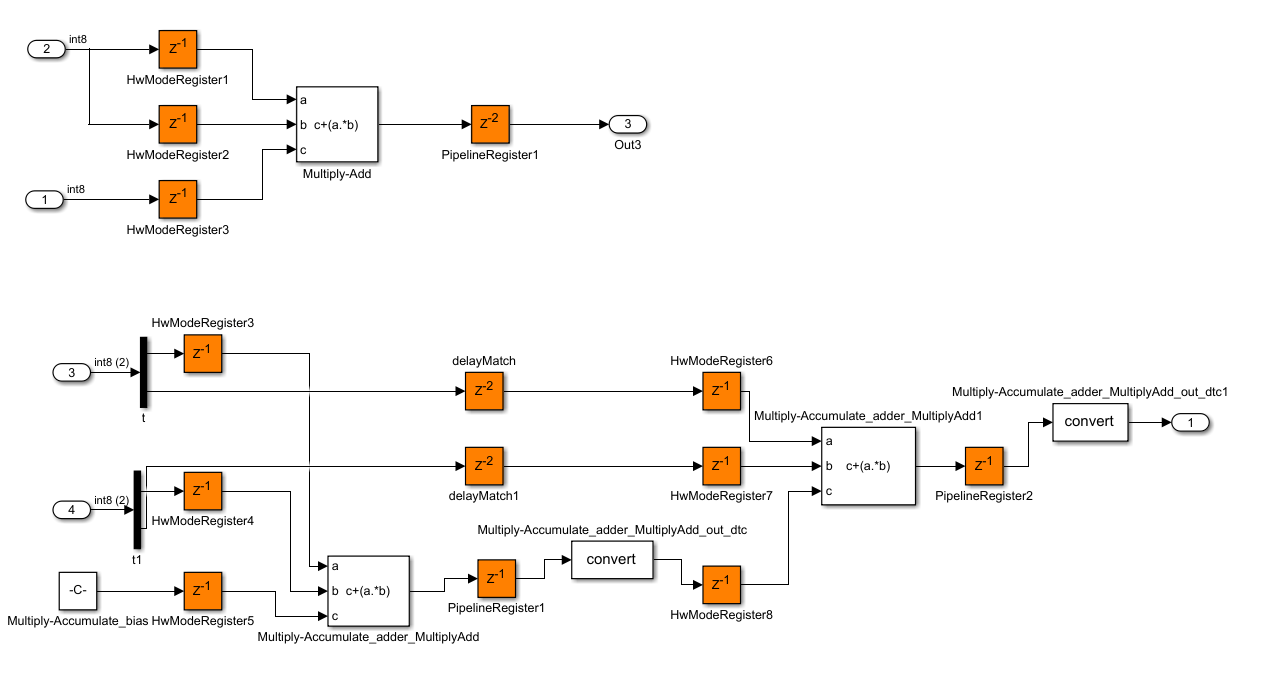

При формировании кода кодер HDL вставляет регистры на входном и выходном портах блоков. Комбинация блоков с регистрами может потенциально отображаться на блоки DSP на целевом устройстве.

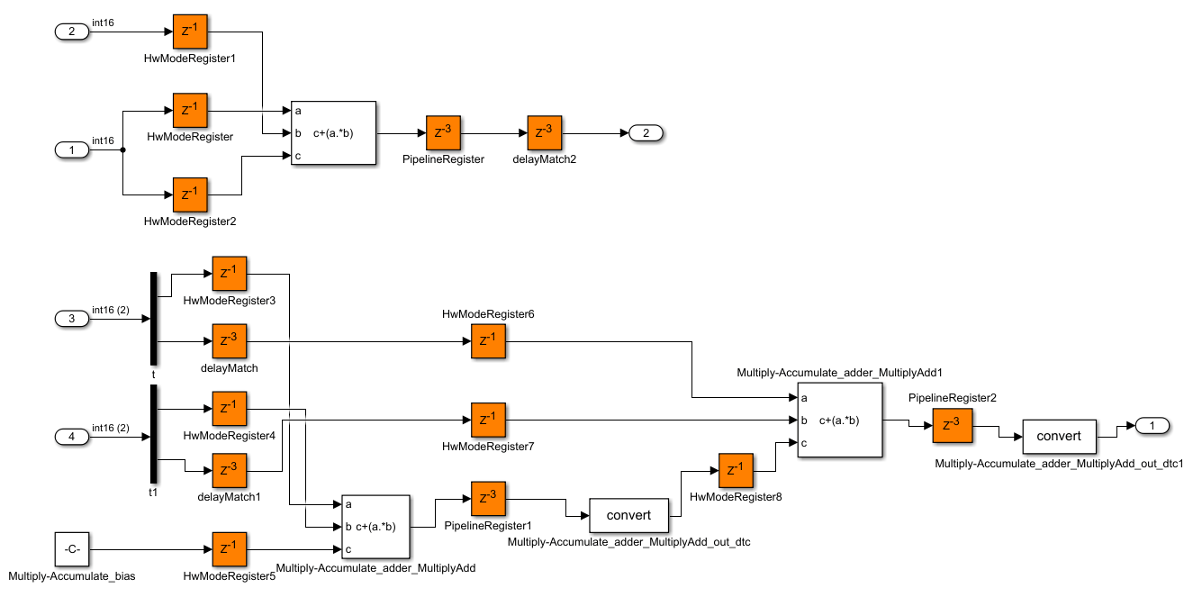

На этом рисунке показана созданная модель для умножения-сложения и умножения-накопления с Intel Arria10 в качестве целевого устройства FPGA и целевой частотой 500 МГц. Входы в блоки имеют тип int8.

Шаблон и количество регистров конвейера, которые вставляет кодер HDL, могут изменяться в зависимости от целевого устройства, целевой частоты и длины слова умножителя.

Этот рисунок представляет собой сгенерированную модель для блоков с Virtex7 Xilinx в качестве целевого устройства FPGA и целевой частотой 1500 МГц. Входные данные имеют тип int16.

Для вставки адаптивных трубопроводов для функциональных блоков MATLAB:

Укажите целевое устройство.

Укажите целевую частоту больше нуля.

Установка архитектуры HDL для функциональных блоков MATLAB в MATLAB Datapath.

Кодер HDL обрабатывает функциональные блоки MATLAB с архитектурой, установленной на MATLAB Datapath как обычные подсистемы. Генератор кода преобразует алгоритм MATLAB ® в блок-схему Simulink ®. Если диаграмма Simulink использует блоки, которые поддерживаются адаптивной конвейерной обработкой, например, Product или Add., генератор кода вставляет регистры конвейера на входной и выходной порты блоков. Комбинация множителей с регистрами может потенциально отображаться на блоки DSP на целевом устройстве.

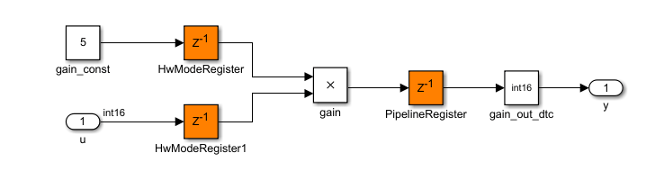

Рассмотрим функциональный блок MATLAB, который использует MATLAB Datapath архитектура. Этот код является алгоритмом внутри функционального блока MATLAB.

function y = fcn(u)

y = u*5;На этом рисунке показана созданная модель функционального блока MATLAB с Intel Arria10 в качестве целевого устройства FPGA и целевой частотой 500 МГц. Входы в блоки имеют тип int16. Генератор кода выводил алгоритм как умножение на константу и вставлял адаптивные конвейеры на входе и выходе.

См. раздел Приложения HDL для функционального блока MATLAB.

Для просмотра информации о адаптивной конвейерной обработке в отчете перед созданием кода для каждой ссылки на подсистему или модель включите отчет «Создание кода». Чтобы включить отчет Создание кода (Code Generation), в диалоговом окне Параметры конфигурации (Configuration Parameters) на панели Создание кода HDL (HDL Code Generation) выберите Генерировать отчет оптимизации (Generate optimization report).

При создании кода кодер HDL создает отчет Создание кода. Выберите раздел «Адаптивная прокладка трубопроводов» в отчете «Оптимизация».

В отчете «Адаптивная конвейерная обработка» отображается состояние адаптивной конвейерной оптимизации и информация о том, вставлял ли кодер HDL адаптивные конвейеры в проект.

Если адаптивная конвейерная обработка выполнена успешно, в отчете отображаются блоки, для которых кодер HDL вставил регистры трубопроводов, количество вставленных регистров трубопроводов и любые дополнительные примечания. Щелкните ссылку на блок, чтобы увидеть регистры трубопровода, вставленные в блоки в проекте.

Если адаптивная конвейерная обработка завершается неуспешно, в отчете отображаются критерии, вызвавшие сбой адаптивной конвейерной обработки.