Операторы временной логики Stateflow ® (например, after, before, или every) - логические операторы, которые работают с счетчиками повторения событий Stateflow. Операторы временной логики могут появляться только в условиях переходов, происходящих из состояний, и в действиях состояний. Хотя временная логика не вводит новые события в модель Stateflow, полезно думать об изменении значения условия временной логики как о событии. Во многих случаях, когда требуется счетчик, можно использовать операторы временной логики. Обычным примером использования является использование временной логики для реализации счетчика тайм-аута.

Дополнительные сведения см. в разделе Управление выполнением диаграммы с помощью временной логики (поток состояний).

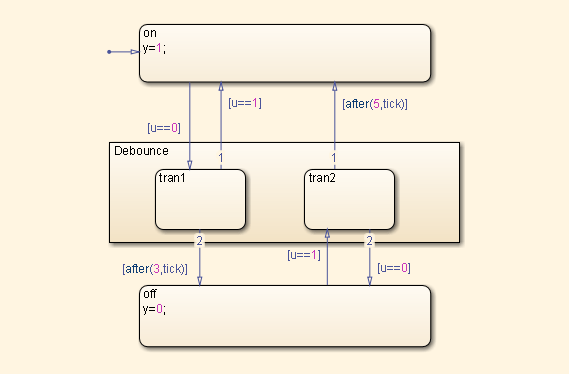

Диаграмма, показанная на следующем рисунке, использует временную логику в конструкции отладчика. Вместо мгновенного переключения между включенными и выключенными состояниями диаграмма использует два промежуточных состояния и временную логику для игнорирования переходных процессов. Переход фиксируется на основе тайм-аута.

По умолчанию состояния в диаграмме Stateflow упорядочиваются в алфавитном порядке. Порядок состояний в коде HDL потенциально может изменяться, если в коде HDL включена генерация порта вывода активного состояния. Чтобы включить этот параметр, откройте окно Свойства диаграммы и установите флажок Создать выходной порт для мониторинга. См. также раздел Упрощение диаграмм статусов путем включения вывода активного состояния (Stateflow).

При создании кода VHDL ® последнее добавленное состояние выбирается в качестве OTHERS состояние в коде HDL. На следующем рисунке показан код VHDL, созданный на основе этой диаграммы.

Chart_1_output : PROCESS (is_Chart, u, temporalCounter_i1, y_reg)

VARIABLE temporalCounter_i1_temp : unsigned(7 DOWNTO 0);

BEGIN

temporalCounter_i1_temp := temporalCounter_i1;

is_Chart_next <= is_Chart;

y_reg_next <= y_reg;

IF temporalCounter_i1 < 7 THEN

temporalCounter_i1_temp := temporalCounter_i1 + 1;

END IF;

CASE is_Chart IS

WHEN IN_tran1 =>

IF u = 1.0 THEN

is_Chart_next <= IN_on;

y_reg_next <= 1.0;

ELSIF temporalCounter_i1_temp >= 3 THEN

is_Chart_next <= IN_off;

y_reg_next <= 0.0;

END IF;

WHEN IN_tran2 =>

IF temporalCounter_i1_temp >= 5 THEN

is_Chart_next <= IN_on;

y_reg_next <= 1.0;

ELSIF u = 0.0 THEN

is_Chart_next <= IN_off;

y_reg_next <= 0.0;

END IF;

WHEN IN_off =>

IF u = 1.0 THEN

is_Chart_next <= IN_tran2;

temporalCounter_i1_temp := to_unsigned(0, 8);

END IF;

WHEN OTHERS =>

IF u = 0.0 THEN

is_Chart_next <= IN_tran1;

temporalCounter_i1_temp := to_unsigned(0, 8);

END IF;

END CASE;

temporalCounter_i1_next <= temporalCounter_i1_temp;

END PROCESS Chart_1_output;Графическая функция - это функция, определяемая графически блок-схемой. Графические функции находятся в диаграмме вместе с вызвавшими их диаграммами. Как и функции MATLAB ® и C, графические функции могут принимать аргументы и возвращать результаты. Графические функции могут быть вызваны в действиях перехода и состояния .

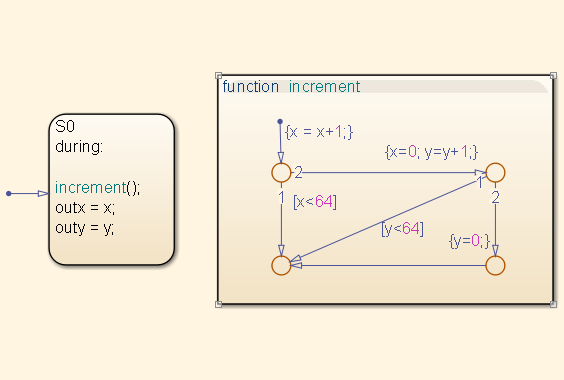

На следующем рисунке показана графическая функция, реализующая счетчик 64 на 64.

На следующем рисунке показан код VHDL, созданный для этой графической функции.

x64_counter_sf : PROCESS (x, y, outx_reg, outy_reg)

-- local variables

VARIABLE x_temp : unsigned(7 DOWNTO 0);

VARIABLE y_temp : unsigned(7 DOWNTO 0);

BEGIN

outx_reg_next <= outx_reg;

outy_reg_next <= outy_reg;

x_temp := x;

y_temp := y;

x_temp := tmw_to_unsigned(tmw_to_unsigned(tmw_to_unsigned(x_temp, 9), 10)

+ tmw_to_unsigned(to_unsigned(1, 9), 10), 8);

IF x_temp < to_unsigned(64, 8) THEN

NULL;

ELSE

x_temp := to_unsigned(0, 8);

y_temp := tmw_to_unsigned(tmw_to_unsigned(tmw_to_unsigned(y_temp, 9), 10)

+ tmw_to_unsigned(to_unsigned(1, 9), 10), 8);

IF y_temp < to_unsigned(64, 8) THEN

NULL;

ELSE

y_temp := to_unsigned(0, 8);

END IF;

END IF;

outx_reg_next <= x_temp;

outy_reg_next <= y_temp;

x_next <= x_temp;

y_next <= y_temp;

END PROCESS x64_counter_sf;Диаграммы потока состояний поддерживают как иерархию (состояния, содержащие другие состояния), так и параллелизм (несколько состояний, которые могут быть активными одновременно).

В семантике Stateflow параллелизм не является синонимом параллелизма. Параллельные состояния могут быть активными одновременно, но они выполняются последовательно в соответствии с их порядком выполнения. (Порядок выполнения отображается в правом верхнем углу параллельного состояния).

Дополнительные сведения об иерархии и параллелизме см. в разделах Иерархия объектов потока состояний (Stateflow) и Порядок выполнения для параллельных состояний (Stateflow).

Для генерации кода HDL вся диаграмма отображается в одном процессе вычисления выходных данных. В процессе вычисления выходных данных:

Выполнение параллельных состояний происходит последовательно.

Вложенные иерархические состояния сопоставляются вложенным CASE операторов в сгенерированном коде HDL.

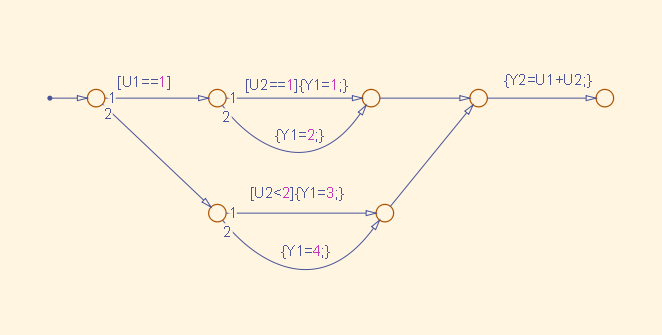

Диаграммы, состоящие из чистых блок-схем (то есть диаграммы без состояний), полезны для захвата if-then-else конструкции, используемые в процедурных языках, таких как C.

В качестве примера рассмотрим следующую логику, выраженную в C-подобном псевдокоде.

if(U1==1) {

if(U2==1) {

Y = 1;

}else{

Y = 2;

}

}else{

if(U2<2) {

Y = 3;

}else{

Y = 4;

}

}

На следующем рисунке показана блок-схема, реализующая if-then-else логика.

Следующий сгенерированный фрагмент кода VHDL показывает вложенные операторы IF-ELSE, полученные из блок-схемы.

Chart : PROCESS (Y1_reg, Y2_reg, U1, U2)

-- local variables

BEGIN

Y1_reg_next <= Y1_reg;

Y2_reg_next <= Y2_reg;

IF unsigned(U1) = to_unsigned(1, 8) THEN

IF unsigned(U2) = to_unsigned(1, 8) THEN

Y1_reg_next <= to_unsigned(1, 8);

ELSE

Y1_reg_next <= to_unsigned(2, 8);

END IF;

ELSIF unsigned(U2) < to_unsigned(2, 8) THEN

Y1_reg_next <= to_unsigned(3, 8);

ELSE

Y1_reg_next <= to_unsigned(4, 8);

END IF;

Y2_reg_next <= tmw_to_unsigned(tmw_to_unsigned(tmw_to_unsigned(unsigned(U1), 9),10)

+ tmw_to_unsigned(tmw_to_unsigned(unsigned(U2), 9), 10), 8);

END PROCESS Chart;HDL Coder™ поддерживает генерацию кода HDL для:

Функции таблицы истинности в диаграмме Stateflow

Блоки таблицы истинности (Stateflow) в моделях Simulink ®

В этом разделе рассматривается функция таблицы истинности в диаграмме и код VHDL, сгенерированный для диаграммы.

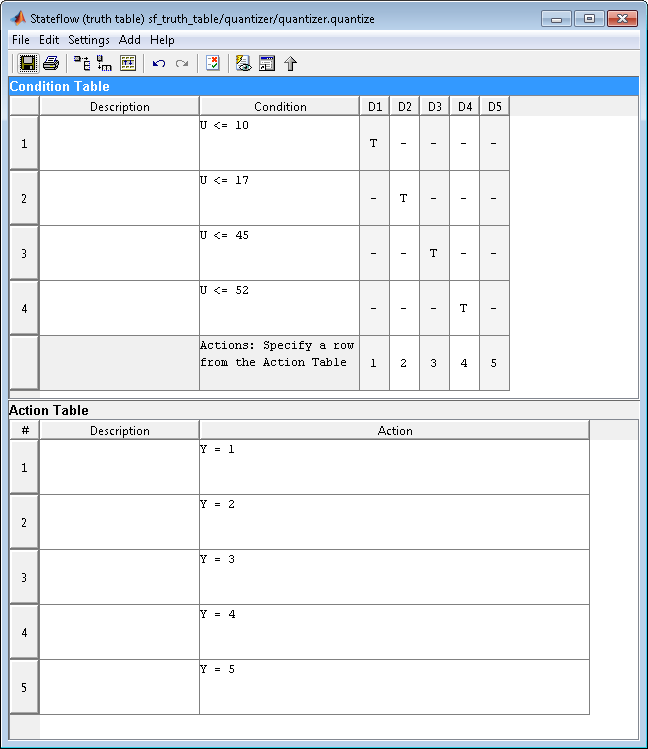

Таблицы истинности хорошо подходят для реализации компактной комбинаторной логики. Типичным приложением для таблиц истинности является реализация нелинейного квантования или пороговой логики. Рассмотрим следующую логику:

Y = 1 when 0 <= U <= 10 Y = 2 when 10 < U <= 17 Y = 3 when 17 < U <= 45 Y = 4 when 45 < U <= 52 Y = 5 when 52 < U

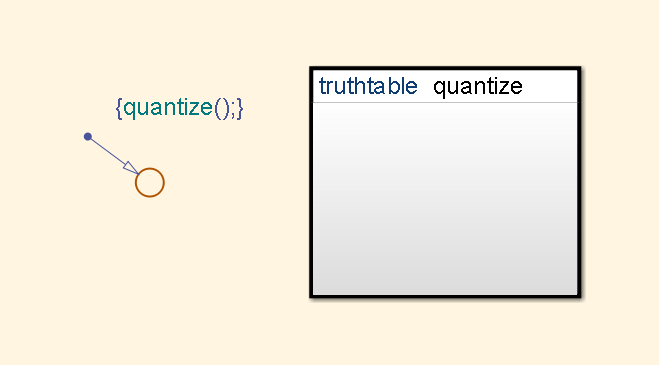

Диаграмма без состояния с единственным вызовом функции таблицы истинности может представить эту логику лаконично.

На следующем рисунке показаны quantizer диаграмма, содержащая таблицу истинности.

На следующем рисунке показана пороговая логика, отображаемая в редакторе таблиц истинности.

Следующий фрагмент кода показывает код VHDL, сгенерированный для quantizer диаграмма.

quantizer : PROCESS (Y_reg, U)

-- local variables

VARIABLE aVarTruthTableCondition_1 : std_logic;

VARIABLE aVarTruthTableCondition_2 : std_logic;

VARIABLE aVarTruthTableCondition_3 : std_logic;

VARIABLE aVarTruthTableCondition_4 : std_logic;

BEGIN

Y_reg_next <= Y_reg;

-- Condition #1

aVarTruthTableCondition_1 := tmw_to_stdlogic(unsigned(U) <= to_unsigned(10, 8));

-- Condition #2

aVarTruthTableCondition_2 := tmw_to_stdlogic(unsigned(U) <= to_unsigned(17, 8));

-- Condition #3

aVarTruthTableCondition_3 := tmw_to_stdlogic(unsigned(U) <= to_unsigned(45, 8));

-- Condition #4

aVarTruthTableCondition_4 := tmw_to_stdlogic(unsigned(U) <= to_unsigned(52, 8));

IF tmw_to_boolean(aVarTruthTableCondition_1) THEN

-- D1

-- Action 1

Y_reg_next <= to_unsigned(1, 8);

ELSIF tmw_to_boolean(aVarTruthTableCondition_2) THEN

-- D2

-- Action 2

Y_reg_next <= to_unsigned(2, 8);

ELSIF tmw_to_boolean(aVarTruthTableCondition_3) THEN

-- D3

-- Action 3

Y_reg_next <= to_unsigned(3, 8);

ELSIF tmw_to_boolean(aVarTruthTableCondition_4) THEN

-- D4

-- Action 4

Y_reg_next <= to_unsigned(4, 8);

ELSE

-- Default

-- Action 5

Y_reg_next <= to_unsigned(5, 8);

END IF;

END PROCESS quantizer;Примечание

При генерации кода для блока таблицы истинности (Stateflow) в модели Simulink кодер HDL записывает отдельный файл объекта/архитектуры для кода таблицы истинности. Имя файла: Truth_Table.vhd (для VHDL) или Truth_Table.v (для Verilog ®).

Просмотр последовательности (поток состояний) | Таблица перехода состояний (поток состояний) | Таблица истинности (поток состояний)