Если модель Simulink ® содержит несколько скоростей выборки или использует оптимизации скорости и площади, которые вставляют регистры трубопроводов, в конструкции могут быть многоцикловые пути. Многоцикловые пути - это пути данных между двумя регистрами, которые работают с частотой дискретизации медленнее, чем тактовая частота FPGA, и поэтому для завершения их выполнения требуется несколько тактовых циклов. Чтобы синхронизировать тактовую частоту с частотой дискретизации различных путей в конструкции, можно использовать один или несколько тактовых режимов. По умолчанию HDL Coder™ использует режим одного тактового сигнала, который генерирует один главный тактовый сигнал с самой высокой частотой дискретизации и создает объект контроллера синхронизации для управления тактовой частотой многоцикловых трактов. Контроллер синхронизации генерирует набор тактовых импульсов, позволяющих с требуемой скоростью и информацией о фазе управлять последовательными элементами, такими как блоки задержки, которые работают с различными скоростями дискретизации.

При синтезировании сгенерированного кода HDL инструменты синтеза могут не соответствовать требованиям синхронизации многоцикловых трактов. Сбой синхронизации происходит из-за того, что инструменты синтеза не могут вывести различные частоты дискретизации в конструкции из сгенерированного кода HDL. Инструменты синтеза предполагают, что регистры в конструкции работают с основной тактовой частотой и требуют, чтобы данные перемещались между регистрами в течение одного тактового цикла. Однако многоцикловые тракты не требуются для завершения их выполнения в течение одного тактового цикла и, следовательно, не могут соответствовать требованиям синхронизации. Для соответствия требованиям синхронизации укажите генерацию ограничений многоциклового тракта на основе включения.

Инструменты синтеза требуют, чтобы данные распространялись от исходного регистра к целевому регистру в течение одного тактового цикла. Ограничения многоциклового тракта ослабляют это требование синхронизации, позволяя нескольким циклам синхронизации данных распространяться между регистрами. Генератор кода использует сигналы разрешения контроллера синхронизации для создания групп регистров, основанных на включении, с регистрами в каждой группе, управляемыми одним и тем же включением синхронизации. При применении ограничений на основе включения и создании кода HDL генератор кода выводит файл ограничений с соглашением об именовании dutname_constraints. Файл определяет требования к синхронизации для многоцикловых трактов и содержит информацию об ограничениях настройки и удержания, которые должны быть выполнены.

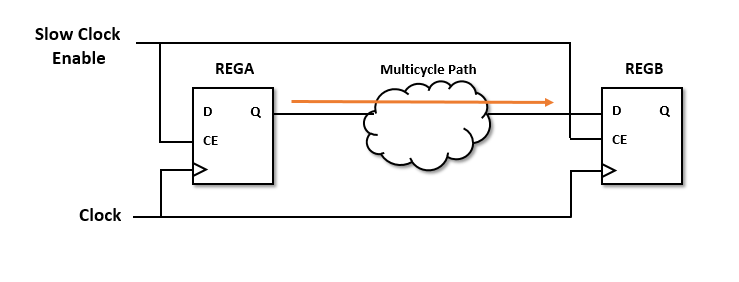

На этом рисунке показан многоцикловый путь, который занимает определенное количество тактовых циклов, скажем N, для данных для распространения из REGA кому REGB. По умолчанию инструменты синтеза определяют границу установки на следующем активном рубеже синхронизации и границу удержания на том же активном фронте синхронизации по отношению к сигналу синхронизации назначения. Для многоцикловой траектории, которая занимает N тактовые циклы, ограничения переопределяют установку и границу хранения, чтобы обеспечить более длительное время распространения данных.

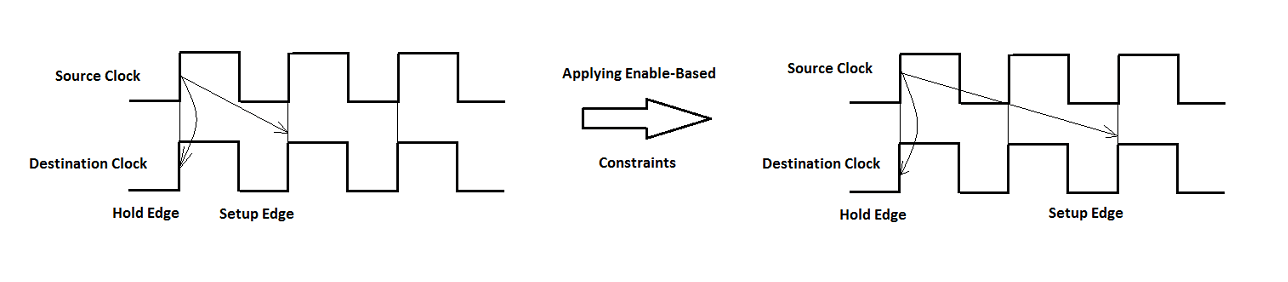

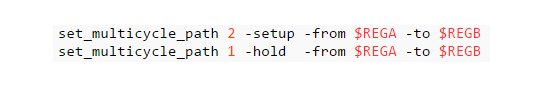

Например, рассмотрим многоцикловой путь, который занимает два тактовых цикла для распространения данных сверху от источника к регистру назначения. Этот сигнал показывает, как применение зависимостей на основе включения переопределяет границы установки и удержания. Этот фрагмент кода показывает это требование настройки и хранения в файле ограничений, который создается при включении ограничений многоциклового пути.

Перед созданием зависимостей на основе включения необходимо выполнить следующие действия.

Сохраните многоцикловые пути в конструкции. Прежде чем включить генерацию ограничений многоциклового пути, убедитесь, что такие оптимизации, как конвейерирование тактовой частоты и адаптивное конвейерирование, отключены в тех областях, где требуется применить ограничения многоциклового пути.

Убедитесь, что область, которая работает с более низкой тактовой частотой, ограничена сигналами разрешения тактового сигнала на основе контроллера синхронизации, работающими на нулевой фазе.

Укажите инструмент «Синтез». Формат создаваемого файла ограничений многоцикловых путей зависит от указанного инструмента синтеза. Если инструмент синтеза не указан и установлен флажок Генерировать сценарии EDA (Generate EDA Scripts), кодер HDL не создает ограничения многоциклового пути.

Используйте режим одиночного синхросигнала. На панели «Создание кода HDL» > «Глобальные параметры» установите для параметра «Входы часов» значение Single.

Генерацию многоцикловых ограничений можно задать в диалоговом окне Параметры конфигурации (Configuration Parameters), в пользовательском интерфейсе помощника по рабочим процессам HDL (HDL Workflow Advisor) или в командной строке.

В диалоговом окне Параметры конфигурации (Configuration Parameters) на панели Создание кода HDL (HDL Code Generation) > Цель и оптимизация (Target and Optimizations) установите флажок Включить ограничения на основе (Enable based constraints).

В помощнике по рабочим процессам HDL установите флажок Включить ограничения на основе (Enable based constraints) в задаче Создание кода HDL (HDL Code Generation > Set Code Generation Options > Set Optimization Options).

В командной строке используйте команду MulticyclePathConstraints свойство с hdlset_param или makehdl.

Если инструменты синтеза определяют ограничения многоцикловой траектории, можно:

Увеличьте тактовую частоту и увеличьте время проектирования.

Уменьшите площадь на целевом устройстве FPGA, так как ограничения многоциклового пути не вводят регистры трубопровода.

Сократите время генерации кода HDL, поскольку генератору кода не требуется запускать множество параметров оптимизации.

Сократите время синтеза, поскольку ограничения многоциклового тракта ослабляют требования к синхронизации инструмента синтеза.

Пропустите проверку конструкции после создания кода HDL, поскольку создаваемая модель с ограничениями идентична исходной модели.

При указании информации о пути к мультициклу для инструмента синтеза не рекомендуется использовать параметр «Регистрация для регистрации информации о пути» на панели «Цель и оптимизация». При использовании этого параметра генератор кода выводит текстовый файл, описывающий информацию о пути к многоциклу в формате, который не является родным для определенного инструмента синтеза. Необходимо преобразовать эту информацию в формат ограничений многоцикловой траектории, требуемый инструментом синтеза.

При использовании настройки зависимостей на основе включения:

Сгенерированные ограничения более устойчивы к именованию изменений в инструментах синтеза.

Генерация кода HDL выполняется быстрее, чем при использовании параметра Register-to-register path info.

Целевой рабочий процесс может быть Generic ASIC/FPGA, FPGA Turnkey, IP Core Generation, и Simulink Real-Time FPGA I/O.

Формат файла ограничений поддерживается Xilinx ISE, Xilinx Vivado, и Altera QUARTUS II.

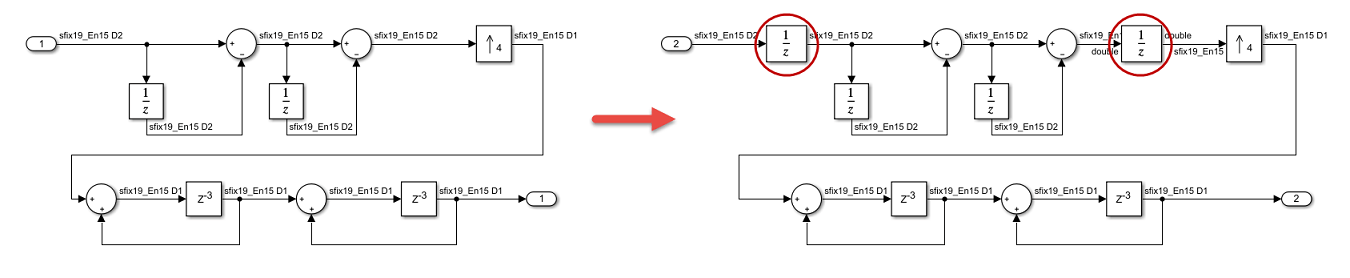

При задании генерации зависимостей на основе включения используйте эти шаблоны моделирования в конструкции. Если модель содержит области с медленной скоростью, которые не ограничены регистрами, добавьте задержки с той же медленной скоростью к входу и выходу областей с медленной скоростью. Например, при вводе hdlcoder_clockdemo в командной строке в MATLAB ® отображается многоскоростной фильтр интерполяции CIC, реализованный в режиме одиночной синхронизации. На этом рисунке показано, как ограничить вход и выход области медленной скорости, аннотированной временем медленной выборкиD2 в модели с блоками единичной задержки, чтобы ограничения на основе включения могли идентифицировать путь медленной скорости.

Примечание

Блоки Rate Transition можно использовать для ввода входных и выходных регистров, но убедитесь, что регистры являются медленными и имеют нулевую фазу.

Ограничения многоциклового пути на основе включения имеют различные форматы файлов, зависящие от указанного инструмента синтеза.

Кодер HDL генерирует ограничения в виде SDC файл. Этот фрагмент кода показывает SDC создан для Altera ® Quartus ® II.

# Multicycle constraints for clock enable: DUT_tc.u1_d4_o0 set enbreg [get_registers *u_DUT_tc|phase_0] set_multicycle_path 4 -to [get_fanouts $enbreg -through [get_pins -hier *|ena]] -end -setup set_multicycle_path 3 -to [get_fanouts $enbreg -through [get_pins -hier *|ena]] -end -hold

Кодер HDL генерирует ограничения в виде XDC файл. Этот фрагмент кода показывает XDC создан для Xilinx ® Vivado ®.

# Multicycle constraints for clock enable: DUT_tc.u1_d4_o0

set enbregcell [get_cells -hier -filter {mcp_info=="DUT_tc.u1_d4_o0"}]

set enbregnet [get_nets -of_objects [get_pins -of_objects $enbregcell -filter {DIRECTION == OUT}]]

set reglist [get_cells -of [filter [all_fanout -flat -endpoints_only $enbregnet] IS_ENABLE]]

set_multicycle_path 4 -setup -from $reglist -to $reglist -quiet

set_multicycle_path 3 -hold -from $reglist -to $reglist -quietОграничения многоциклового пути образуют группы регистров, основанные на включении, путем запроса списка соединений синтеза для ATTRIBUTE ключевое слово. Этот фрагмент кода отображает это ключевое слово в списке соединений синтеза при запуске любого из поддерживаемых целевых рабочих процессов.

... ATTRIBUTE mcp_info: string ATTRIBUTE mcp_info OF phase_0 : SIGNAL IS "DUT_tc.u1_d4_o0"; ...

Кодер HDL генерирует ограничения в виде UCF файл. Этот фрагмент кода показывает UCF файл, генерируемый для модели, которая имеет одну медленную область, управляемую сигналом разрешения синхронизации, и имеет целевую частоту 300MHz. Фрагмент показывает, что ограничения многоцикловой траектории зависят от заданной целевой частоты.

# Multicycle constraints for clock enable: DUT_tc.u1_d4_o0 NET "*u_DUT_tc/phase_0" TNM_NET = FFS "TN_u_DUT_tc_phase_0"; TIMESPEC "TS_u_DUT_tc_phase_0" = FROM "TN_u_DUT_tc_phase_0" TO "TN_u_DUT_tc_phase_0" TS_FPGA_CLK/4;

Этот фрагмент кода показывает ограничения часов, которые генерируются при запуске Generic ASIC/FPGA, FPGA Turnkey, или Simulink Real-Time FPGA I/O workflow-процесс с Xilinx ISE.

# Timing Specification Constraints NET "clk" TNM_NET = "TN_clk"; TIMESPEC "TS_FPGA_CLK" = PERIOD "TN_clk" 300 MHz;

Использование ограничений многоцикльного пути при создании кода HDL с помощью makehdl , убедитесь, что вы добавили TS_FPGA_CLK ограничение для UCF файл.

Файл ограничений многоциклового пути не поддерживается FPGA-in-the-Loop workflow-процесс.

Если область медленной скорости не ограничена регистрами, ограничения многоциклового пути требуют добавления двух блоков задержки с медленной скоростью, что увеличивает задержку проекта.

Генератор кода не добавляет ограничения на тракты между регистрами, которые имеют ненулевое значение фазы для сигналов разрешения на основе контроллера синхронизации. Чтобы генератор кода добавил ограничения, используйте регистры, производные от фазы 0 сигналы включения синхронизации, такие как блоки задержки.

Создаваемые многоцикловые ограничения могут быть менее эффективными, если применяются ограничения в областях с включенной оптимизацией, таких как конвейерная обработка тактовой частоты и адаптивная конвейерная обработка. При конвейере тактовой частоты регистры работают с более высокой тактовой частотой и поэтому могут не сохранять регистры медленной частоты в вашей конструкции.

Кодер HDL не создает ограничения многоциклового пути для односкоростных моделей.

Если используется режим с несколькими часами, генератор кода не выводит файл ограничений многоциклового пути.