Этот раздел содержит параметры на панели «Создание кода HDL» > «Плавающая точка» диалогового окна «Параметры конфигурации». Эти параметры используются для указания стратегии задержки, цели и необходимости инициализации регистров конвейера в целевом IP с плавающей запятой до нуля.

Вставляет дополнительную логику во время генерации кода HDL для инициализации значений регистров конвейера в целевом IP-адресе с плавающей запятой Altera ® до нуля. Если этот флажок не установлен, HDL Coder™ выдает предупреждение во время создания кода HDL.

По умолчанию: Вкл.

Вставляет дополнительную логику для инициализации регистров конвейера в целевом IP-адресе с плавающей запятой до нуля.

Не добавляет дополнительную логику для инициализации регистров конвейера в целевом IP-адресе с плавающей запятой до нуля.

Чтобы задать этот параметр, задайте для библиотеки IP-адресов с плавающей запятой значение Altera Megafunctions (ALTERA FP FUNCTIONS). Перед установкой библиотеки с плавающей запятой укажите путь к инструменту синтеза с помощью hdlsetuptoolpath функция.

Чтобы задать этот параметр, выполните следующие действия.

Создание целевого объекта конфигурации с плавающей запятой с помощью Altera Megafunctions (ALTERA FP FUNCTIONS) в качестве целевой библиотеки с плавающей запятой.

fpconfig = hdlcoder.createFloatingPointTargetConfig('AlteraFPFunctions');Укажите InitializeIPPipelinesToZero имущества LibrarySettings атрибут целевого объекта конфигурации с плавающей запятой.

fpconfig.LibrarySettings.InitializeIPPipelinesToZero = 0;

Задайте конфигурацию цели с плавающей запятой в модели, а затем создайте код HDL. В этом примере показано, как установить конфигурацию на sfir_single модель и сгенерировать код HDL для symmetric_fir подсистема:

hdlset_param('sfir_single','FloatingPointTargetConfig',fpconfig)

makehdl('sfir_single/symmetric_fir')

Укажите, следует ли сопоставлять минимальную или максимальную задержку с IP-адресами Xilinx ® LogiCORE или ALTFP Altera megafunction.

По умолчанию:

MIN

Возможны следующие варианты:

MINСоответствует минимальной задержке для указанного целевого IP-адреса с плавающей запятой.

MAXСоответствует максимальной задержке для указанного целевого IP-адреса с плавающей запятой.

Чтобы задать этот параметр, задайте для библиотеки IP-адресов с плавающей запятой значение Altera Megafunctions (ALTFP) или Xilinx LogiCORE. Перед установкой библиотеки с плавающей запятой укажите путь к инструменту синтеза с помощью hdlsetuptoolpath функция.

Чтобы задать этот параметр, выполните следующие действия.

Создание целевого объекта конфигурации с плавающей запятой с помощью Altera Megafunctions (ALTERA FP FUNCTIONS) в качестве целевой библиотеки с плавающей запятой.

fpconfig = hdlcoder.createFloatingPointTargetConfig('ALTFP');Укажите LatencyStrategy имущества LibrarySettings атрибут целевого объекта конфигурации с плавающей запятой.

fpconfig.LibrarySettings.LatencyStrategy = 'MAX';

Задайте конфигурацию цели с плавающей запятой в модели, а затем создайте код HDL. В этом примере показано, как установить конфигурацию на sfir_single модель и сгенерировать код HDL для symmetric_fir подсистема:

hdlset_param('sfir_single','FloatingPointTargetConfig',fpconfig)

makehdl('sfir_single/symmetric_fir')

Укажите, требуется ли оптимизировать конструкцию для скорости или области при сопоставлении с целевыми библиотеками с плавающей запятой.

По умолчанию:

SPEED

Возможны следующие варианты:

NONEВыберите этот параметр, если не требуется оптимизировать конструкцию для скорости или площади.

SPEEDВыберите этот параметр для оптимизации конструкции по скорости.

AREAВыберите этот параметр, чтобы оптимизировать проект для области.

Чтобы задать этот параметр, задайте для библиотеки IP-адресов с плавающей запятой значение Altera Megafunctions (ALTFP) или Xilinx LogiCORE. Перед установкой библиотеки с плавающей запятой укажите путь к инструменту синтеза с помощью hdlsetuptoolpath функция.

Чтобы задать этот параметр, выполните следующие действия.

Создание целевого объекта конфигурации с плавающей запятой с помощью Altera Megafunctions (ALTERA FP FUNCTIONS) в качестве целевой библиотеки с плавающей запятой.

fpconfig = hdlcoder.createFloatingPointTargetConfig('ALTFP');Укажите Objective имущества LibrarySettings атрибут целевого объекта конфигурации с плавающей запятой.

fpconfig.LibrarySettings.Objective = 'AREA';

Задайте конфигурацию цели с плавающей запятой в модели, а затем создайте код HDL. В этом примере показано, как установить конфигурацию на sfir_single модель и сгенерировать код HDL для symmetric_fir подсистема:

hdlset_param('sfir_single','FloatingPointTargetConfig',fpconfig)

makehdl('sfir_single/symmetric_fir')

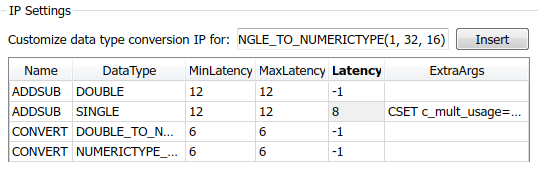

В разделе «IP Settings» имеется таблица конфигурации IP-адресов с именами IP-адресов и типами данных, а также дополнительные параметры, определяющие пользовательскую задержку и дополнительные аргументы.

Параметры в таблице IP-конфигурации зависят от указанной библиотеки.

При указании ALTERA MEGAFUNCTION (ALTERA FP FUNCTIONS) библиотека, кодер HDL выводит значение задержки из значения целевой частоты (МГц).

При указании ALTERA MEGAFUNCTION (ALTFP) или XILINX LOGICORE библиотеки, кодер HDL выводит задержку IP из параметра «Стратегия задержки». Таблица конфигурации IP содержит два дополнительных столбца, MinLatency и MaxLatency, которые содержат минимальное и максимальное значения задержки для каждого IP в таблице.

Таблица IP-конфигурации содержит следующие разделы:

Имя: Содержит список IP-имен, которым кодер HDL сопоставляет блоки Simulink ®, например ABS, ADDSUB, и CONVERT.

DataType: содержит список типов IP-данных для каждого IP-адреса в таблице. Это в основном SINGLE и DOUBLE типы данных. CONVERT IP-блоки могут иметь DOUBLE_TO_NUMERICTYPE, NUMERICTYPE_TO_DOUBLE типы данных и т. д.

Задержка: значение задержки по умолчанию: –1 означает, что IP наследует значение задержки от целевой частоты или настройки стратегии задержки в зависимости от выбранной библиотеки. Чтобы настроить задержку IP-адреса, с которым сопоставляются блоки Simulink, введите собственное пользовательское значение задержки.

ExtraArgs: Укажите любые дополнительные параметры, относящиеся к IP.

Например, при наличии блока «Добавить» с Single типы данных в модели Simulink, HDL Coder сопоставляет блок с ADDSUB IP. Если необходимо указать пользовательское значение задержки, например 8, для IP, введите значение в столбце Задержка для IP.

cmultusage - параметр, который можно указать с помощью библиотек Xilinx LogiCORE ®.

Чтобы задать этот параметр, задайте для библиотеки IP-адресов с плавающей запятой значение Altera Megafunctions (ALTFP) или Xilinx LogiCORE. Перед установкой библиотеки с плавающей запятой укажите путь к инструменту синтеза с помощью hdlsetuptoolpath функция.

Чтобы задать этот параметр, выполните следующие действия.

Создание целевого объекта конфигурации с плавающей запятой с помощью Altera Megafunctions (ALTERA FP FUNCTIONS) в качестве целевой библиотеки с плавающей запятой.

fpconfig = hdlcoder.createFloatingPointTargetConfig('ALTFP');Для просмотра IP-конфигурации с плавающей запятой используйте IPConfig объект.

fpconfig.IPConfig

Чтобы настроить задержку или указать дополнительные аргументы, используйте customize способ.

fpconfig.IPConfig.customize('ADDSUB','Single','Latency',6);Задайте конфигурацию цели с плавающей запятой в модели, а затем создайте код HDL. В этом примере показано, как установить конфигурацию на sfir_single модель и сгенерировать код HDL для symmetric_fir подсистема:

hdlset_param('sfir_single','FloatingPointTargetConfig',fpconfig)

makehdl('sfir_single/symmetric_fir')