Если имеются блоки с состоянием и включены или сброшены порты в подсистеме, используйте Synchronous режим блока Госконтроля для:

Обеспечение эффективного включения и сброса моделирования на оборудовании.

Создание более чистого кода HDL и использование меньшего количества ресурсов на оборудовании.

Блок управления состоянием можно добавить в модель Simulink ® на любом уровне иерархии модели. Установка блока управления состоянием влияет на поведение моделирования других блоков в подсистеме, имеющих состояние.

Для синхронного аппаратного моделирования установите для параметра State control значение Synchronous.

Для моделирования Simulink по умолчанию установите для параметра Управление состоянием значение Classic.

| Функциональность | Синхронный режим | Классический режим |

|---|---|---|

| Установка блока управления состоянием | Установка блока по умолчанию при добавлении блока из библиотеки блоков подсистем HDL. | Поведение моделирования совпадает с поведением подсистемы, не использующей блок управления состоянием. |

Поведение симулятора

| Метод обновления обновляет только состояния. Метод вывода вычисляет выходные значения на каждом временном шаге. Например, при включении подсистем выходное значение изменяется, когда разрешающий сигнал является низким при обработке новых входных значений. Выходное значение соответствует выходному значению | Метод обновления обновляет состояния и вычисляет выходные значения. Например, при включенной подсистеме выходное значение сохраняется постоянным, когда разрешающий сигнал является низким, и изменяется, только когда разрешающий сигнал становится высоким. |

| Поведение при моделировании HDL | Повышение эффективности аппаратного обеспечения. | Менее эффективно на аппаратном обеспечении. |

| Поведение при генерации кода HDL | Созданный код HDL является более чистым и использует меньше ресурсов на оборудовании. Например, если включены подсистемы, HDL Coder™ не создает байпасные регистры для каждого обновления состояния и использует меньше аппаратных ресурсов. | Сгенерированный код HDL не является чистым и использует больше аппаратных ресурсов. Например, после включения подсистем кодер HDL создает байпасные регистры для каждого обновления состояния и использует больше ресурсов. |

Дополнительные сведения о том, когда можно использовать блок государственного контроля, см. в разделе Государственный контроль.

Чтобы узнать, использует ли подсистема в модели Simulink синхронную семантику:

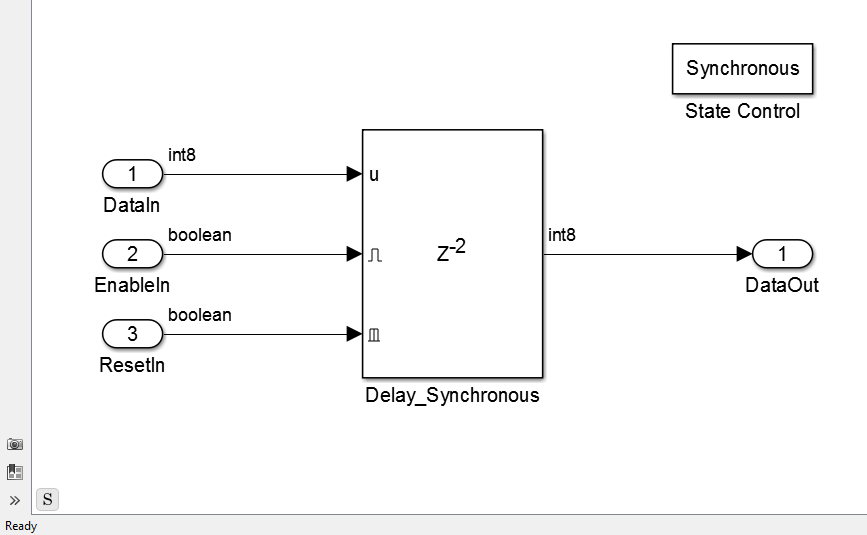

На подсистеме отображается символ S, указывающий на синхронное поведение.

Если дважды щелкнуть подсистему SynchronousStateControl, в редакторе Simulink отобразится значок S, указывающий, что блоки внутри подсистемы используют синхронную семантику оборудования.

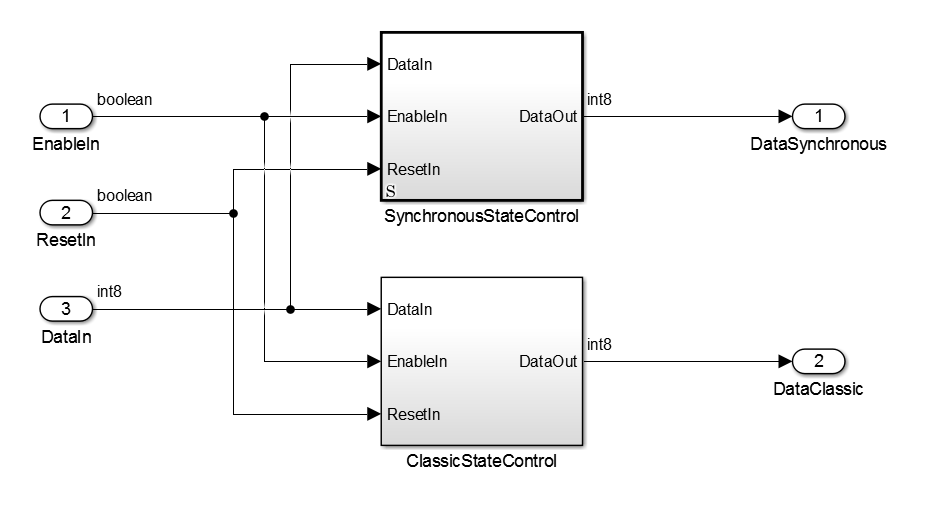

Подсистемы SynchronousStateControl и ClassicStateControl используют блок задержки с внешним сбросом и портом включения в Synchronous и Classic соответственно.

В следующей таблице показано сравнение кода HDL, сгенерированного из блока задержки для Classic и Synchronous режимы блока Госконтроля.

| Функциональность | Синхронный режим | Классический режим |

|---|---|---|

Формирование кода HDL. Применены параметры:

|

`timescale 1 ns / 1 ns

module SynchronousStateControl

(

clk,

reset,

enb,

DataIn,

EnableIn,

ResetIn,

DataOut

);

input clk;

input reset;

input enb;

input signed [7:0] DataIn; // int8

input EnableIn;

input ResetIn;

output signed [7:0] DataOut; // int8

reg signed [7:0] Delay_Synchronous_reg [0:1]; // sfix8 [2]

wire signed [7:0] Delay_Synchronous_reg_next [0:1]; // sfix8 [2]

wire signed [7:0] Delay_Synchronous_out1; // int8

always @(posedge clk)

begin : Delay_Synchronous_process

if (reset == 1'b1 || ResetIn == 1'b1) begin

Delay_Synchronous_reg[0] <= 8'sb00000000;

Delay_Synchronous_reg[1] <= 8'sb00000000;

end

else begin

if (enb && EnableIn) begin

Delay_Synchronous_reg[0] <= Delay_Synchronous_reg_next[0];

Delay_Synchronous_reg[1] <= Delay_Synchronous_reg_next[1];

end

end

end

assign Delay_Synchronous_out1 = Delay_Synchronous_reg[1];

assign Delay_Synchronous_reg_next[0] = DataIn;

assign Delay_Synchronous_reg_next[1] = Delay_Synchronous_reg[0];

assign DataOut = Delay_Synchronous_out1;

endmodule // SynchronousStateControl

|

`timescale 1 ns / 1 ns

module ClassicStateControl

(

clk,

reset,

enb,

DataIn,

EnableIn,

ResetIn,

DataOut

);

input clk;

input reset;

input enb;

input signed [7:0] DataIn; // int8

input EnableIn;

input ResetIn;

output signed [7:0] DataOut; // int8

reg signed [7:0] Delay_Synchronous_bypass; // sfix8

reg signed [7:0] Delay_Synchronous_reg [0:1]; // sfix8 [2]

wire signed [7:0] Delay_Synchronous_bypass_next; // sfix8

wire signed [7:0] Delay_Synchronous_reg_next [0:1]; // sfix8 [2]

wire signed [7:0] Delay_Synchronous_delay_out; // sfix8

wire signed [7:0] Delay_Synchronous_out1; // int8

always @(posedge clk)

begin : Delay_Synchronous_process

if (reset == 1'b1 || ResetIn == 1'b1) begin

Delay_Synchronous_bypass <= 8'sb00000000;

Delay_Synchronous_reg[0] <= 8'sb00000000;

Delay_Synchronous_reg[1] <= 8'sb00000000;

end

else begin

if (enb && EnableIn) begin

Delay_Synchronous_bypass <= Delay_Synchronous_bypass_next;

Delay_Synchronous_reg[0] <= Delay_Synchronous_reg_next[0];

Delay_Synchronous_reg[1] <= Delay_Synchronous_reg_next[1];

end

end

end

assign Delay_Synchronous_delay_out = (ResetIn == 1'b1 ? 8'sb00000000 :

Delay_Synchronous_reg[1]);

assign Delay_Synchronous_out1 = (EnableIn == 1'b1 ? Delay_Synchronous_delay_out :

Delay_Synchronous_bypass);

assign Delay_Synchronous_bypass_next = Delay_Synchronous_delay_out;

assign Delay_Synchronous_reg_next[0] = DataIn;

assign Delay_Synchronous_reg_next[1] = Delay_Synchronous_reg[0];

assign DataOut = Delay_Synchronous_out1;

endmodule // ClassicStateControl

|

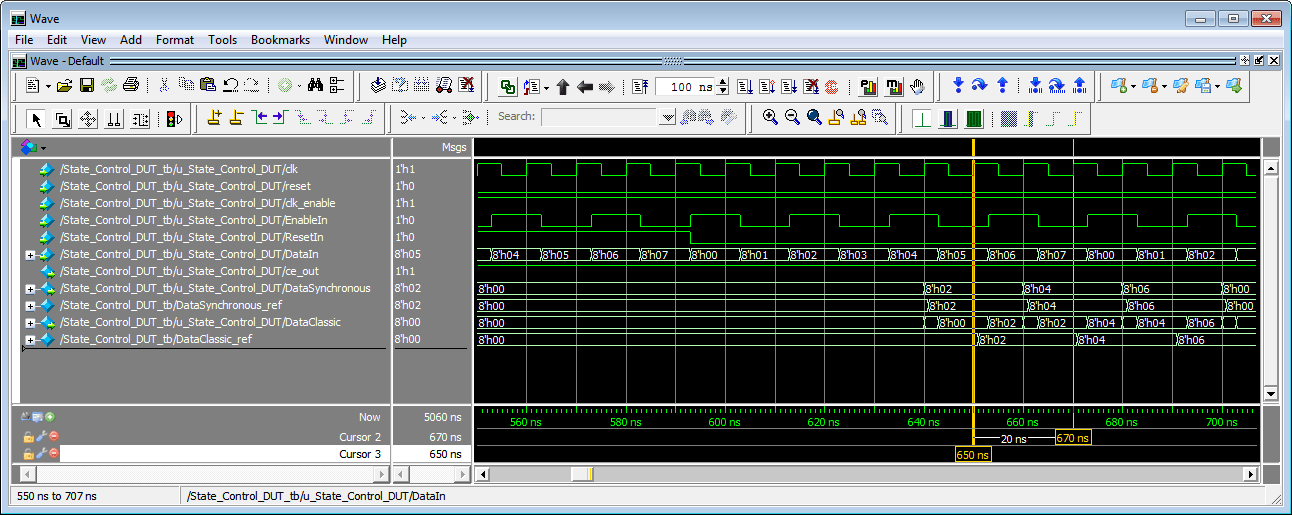

См. вышеприведенную модель Simulink, которая показывает блок задержки, использующий Classic и Synchronous режимы блока Госконтроля. На следующей диаграмме показано поведение моделирования ModelSim ® для блока задержки.

При высоком уровне сигнала ResetIn сигналы DataClassic и DataSynchronous выдают одинаковый выходной сигнал.

Когда сигналы ResetIn и EnureIn являются низкими, сигнал DataSynchronous сохраняет свое значение и изменяется только тогда, когда сигнал EnureIn становится высоким на следующем активном рубеже синхронизации. Значения сигнала DataClassic изменяются при низком уровне сигнала EnureIn при обработке новых входных значений. Значения сигнала DataClassic соответствуют значениям сигнала DataSynchronous, когда значение EnureIn становится высоким.

Сведения о создании кода HDL и моделировании конструкции в ModelSim см. в разделе Создание кода HDL из модели Simulink.