В этом примере показано, как можно создать код HDL для простой модели счетчика в Simulink ®. Эта модель совместима с генерацией кода HDL. Чтобы создать эту модель счетчика, см. раздел Создание модели Simulink, совместимой с HDL.

Можно либо создать собственную модель, совместимую с ЛПВП, например модель счетчика, либо выбрать один из следующих вариантов:

Примеры моделей HDL Coder™ доступны в hdlcoderdemos папка.

cd (fullfile(matlabroot,'toolbox','hdlcoder','hdlcoderdemos'))

Эти модели доступны на пути MATLAB ®. Например, можно выбрать симметричную модель фильтра КИХ (FIR Filter Model). Для использования этой модели введите:

sfir_fixed

Шаблоны Simulink для генерации кода HDL. Шаблоны можно использовать для моделирования регистров, ПЗУ, базовых арифметических операций, комплексных множителей, регистров сдвига и т.д.

Чтобы выбрать шаблон, на панели инструментов MATLAB нажмите![]() кнопку и перейдите в раздел Кодер HDL. См. раздел Использование шаблонов Simulink для создания кода HDL.

кнопку и перейдите в раздел Кодер HDL. См. раздел Использование шаблонов Simulink для создания кода HDL.

Перед созданием кода HDL можно проверить и обновить модель на совместимость с HDL с помощью помощника по коду HDL. См. раздел Проверка совместимости HDL модели Simulink с помощью помощника по кодам HDL.

Откройте эту модель, чтобы увидеть простой счетчик. Модель подсчитывается от нуля до порогового значения, а затем возвращается к нулю. Пороговое значение устанавливается равным 15. Чтобы изменить пороговое значение, измените значение ввода на count_threshold порт. Сигнал Enable указывает, имеет ли счетчик предыдущее значение. Значение 1 указывает, что счетчик постоянно подсчитывается вверх.

Для модели счетчика HDL_DUT подсистема является DUT. Чтобы создать код для DUT:

На вкладке Приложения выберите Кодер HDL.

Выберите подсистему DUT в модели и убедитесь, что это имя подсистемы отображается в опции Код для на вкладке Код HDL. Чтобы запомнить выбор, закрепите этот параметр. Щелкните Создать код HDL (Generate HDL Code).

По умолчанию кодер HDL генерирует код VHDL в целевом объекте hdlsrc папка.

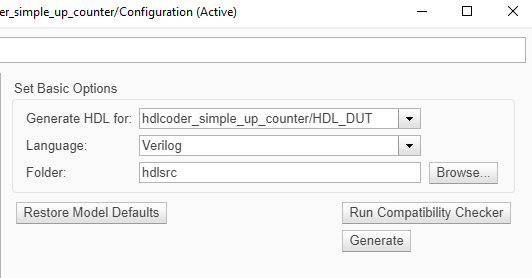

Чтобы создать код Verilog для модели счетчика:

На вкладке Код HDL (HDL Code) щелкните Настройки (Settings).

На панели «Создание кода HDL» в поле «Язык» выберите Verilog. Щелкните Применить (Apply), а затем Создать (Generate).

Кодер HDL компилирует модель перед созданием кода. В зависимости от опций отображения модели, таких как типы данных портов, модель может изменяться в виде после генерации кода. По мере формирования кода кодер HDL отображает сообщения о ходе выполнения в командной строке MATLAB со ссылками на набор конфигурации и сгенерированные файлы. Чтобы просмотреть файлы в редакторе MATLAB, щелкните ссылки.

Процесс завершен и отображается следующее сообщение:

### HDL Code Generation Complete.

Значок папки для hdlsrc отображается в текущей папке. Для просмотра созданных файлов кода и сценариев дважды щелкните значок hdlsrc затем дважды щелкните папку, имя которой совпадает с именем модели, для которой был создан код HDL.

HDL_DUT.vhd: Код VHDL ®, содержащий определение сущности и архитектуру RTL, реализующую спроектированный счетчик. Если вы создали код Verilog, вы получите HDL_DUT.v файл.

HDL_DUT_compile.do: Сценарий компиляции Mentor Graphics ® ModelSim ®.

HDL_DUT_map.txt: Отображение файла, который сопоставляет сгенерированные объекты или модули в коде HDL с подсистемами в модели, которые их создали. См. раздел Трассировка кода с использованием файла сопоставления.

HDL_DUT_report.html: Отчет о проверке HDL отображает состояние генерации кода HDL и предупреждения или сообщения.

gm_hdlcoder_simple_up_counter.slx: Созданная модель, которая поведенчески представляет код HDL в среде моделирования Simulink.

Кодер HDL создает поведенческую модель кода HDL, называемую сгенерированной моделью. Имя созданной модели совпадает с именем исходной модели и имеет префикс gm_. Сгенерированная модель является битовой и цикличной по отношению к сгенерированному коду ЛПВП. Эта модель показывает эффект реализации блоков и оптимизации скорости и площади, указанные пользователем. См. также раздел Оптимизация скорости и площади в кодере HDL.

Чтобы открыть созданную модель для счетчика, введите:

gm_hdlcoder_simple_up_counter

Для счетной модели, поскольку оптимизации отключены, создаваемая модель идентична исходной модели.

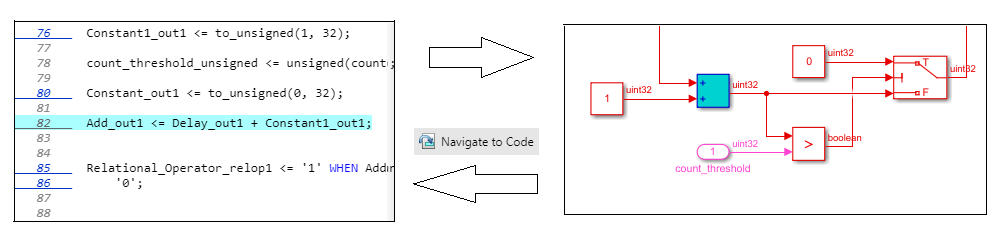

Для упрощения определения соответствия между исходной моделью и сгенерированным кодом HDL создайте отчет об отслеживаемости. Используйте отчет для перехода от блока в модели к сгенерированному коду для этого блока и от кода к блоку в модели.

Чтобы создать отчет об отслеживаемости:

На вкладке Код HDL (HDL Code) щелкните Настройки (Settings) > Параметры отчета (Report Options).

На панели Создание кода HDL (HDL Code Generation) > Отчет (Report) выберите Создать отчет об отслеживании (Generate traceability report), а затем создайте код HDL для HDL_DUT подсистема

После создания кода откроется окно Отчет о создании кода (Code Generation Report). Кодер HDL записывает файлы отчетов о генерации кода в hdlsrc\html\ папки сборки. При закрытии отчета можно перейти в эту папку для повторного открытия отчета.

Для перехода от кода HDL к модели:

В окне Отчет о создании кода (Code Generation Report) перейдите в раздел Отчет об отслеживании (Traceability Report), а затем щелкните ссылки в разделе Расположение кода (Code Location).

Выберите гиперссылку на строку кода, чтобы выделить соответствующий блок в модели.

Чтобы перейти от блока модели к коду HDL, выберите этот блок и нажмите кнопку «Перейти к коду» в разделе «Результаты проверки» вкладки «Код HDL».

См. разделы Навигация между моделью Simulink и кодом HDL с помощью отслеживания и Создание и использование отчетов о создании кода.

Если щелкнуть файл HDL в разделе Сгенерированные исходные файлы HDL_DUT, вы видите сигналы clk, reset, и clk_enable. Эти сигналы являются синхросигналами, сбросом и включением синхросигналов, которые управляют триггерами на целевых аппаратных средствах. Кодер HDL генерирует эти сигналы в коде в зависимости от последовательных элементов, таких как блоки задержки, которые используются в модели. См. раздел Генерация сигналов синхросигналов в кодере HDL.

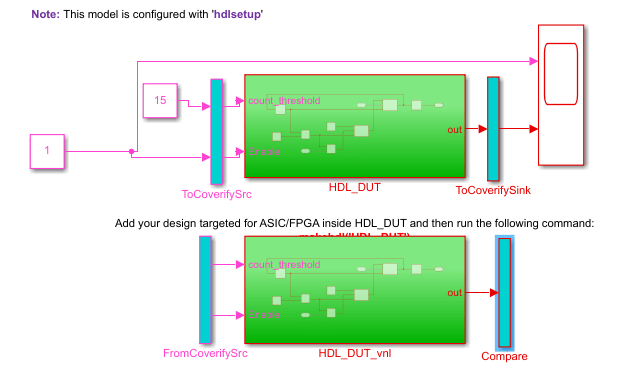

Чтобы проверить поведенческую модель кода HDL с помощью исходной модели, создайте модель проверки. Модель проверки содержит как исходную, так и сгенерированную модель. Он сравнивает выходные данные обеих моделей с использованием тестовых векторов, предоставленных в исходной модели.

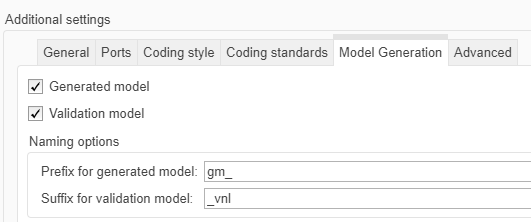

Чтобы создать модель проверки, выполните следующие действия.

На вкладке Код HDL (HDL Code) щелкните Настройки (Settings).

На вкладке Создание кода HDL > Глобальные настройки > Создание модели выберите Модель проверки, а затем создайте код HDL для HDL_DUT подсистема.

В журналах создания кода отображается ссылка на модель проверки. Модель проверки имеет тот же префикс, что и созданная модель, а также суффикс _vnl. Для модели счетчика модель проверки имеет имя gm_hdlcoder_simple_up_counter_vnl.slx. Эту модель можно найти в той же папке, что и созданную модель. Чтобы открыть эту модель, введите:

gm_hdlcoder_simple_up_counter_vnl

После моделирования модели дважды щелкните значок Compare , а затем перейдите внутрь Assert_Out подсистема. При открытии блока «Scope» будет видно, что err сигнал имеет нулевое значение, что означает, что сформированный выходной сигнал модели соответствует исходной модели.

Перед развертыванием проекта на целевом оборудовании проверьте созданный код HDL. От hdlsrc перейдите к текущей рабочей папке. См. раздел Проверка сгенерированного кода HDL из модели Simulink.

hdlset_param | hdlsetup | makehdl