Рекомендуется использовать эти рекомендуемые параметры при иерархическом построении модели и создании кода HDL для проекта. Каждое руководство имеет уровень серьезности, который указывает уровень соответствия требованиям. Дополнительные сведения см. в разделе Рекомендации по моделированию HDL Уровни серьезности.

Идентификатор руководства

1.2.4

Серьезность

Обязательный

Описание

Рекомендуется избегать прямого подключения блоков констант к портам вывода подсистемы. Инструменты синтеза могут оптимизировать и удалить константы и создать неподключенные порты.

При использовании типов данных с плавающей запятой с Native Floating Point включение режима и ввод значений констант в арифметический оператор, такой как блок Add, HDL Coder™ заменяет блок Add блоком Constant при создании кода. Эта оптимизация может привести к тому, что блок константы будет непосредственно подключен к выходному порту. Поэтому рекомендуется избегать таких конструкций моделирования. См. также раздел Упрощение постоянных операций и снижение сложности проектирования в кодере HDL.

Например, откройте модель hdlcoder_constant_subsystem_boundary.slx. DUT содержит две подсистемы Constant_subsys1 и Constant_subsys2, выходы которых являются входами в третью подсистему. Constant_subsys1 содержит блоки констант, непосредственно подключенные к портам вывода, и Constant_subsys2 Содержит блоки констант, которые имеют один тип данных в качестве входных данных для блока Add.

load_system('hdlcoder_constant_subsystem_boundary.slx') set_param('hdlcoder_constant_subsystem_boundary','SimulationCommand','Update') open_system('hdlcoder_constant_subsystem_boundary/DUT/Constant_subsys1')

open_system('hdlcoder_constant_subsystem_boundary/DUT/Constant_subsys2')

Как Constant_subsys2 использует отдельные типы данных, и модель имеет Native Floating Point режим включен, при генерации кода HDL для DUT, Constant_subsys2 становится кандидатом на оптимизацию, которая упрощает постоянные операции. При открытии созданной модели отображается блок константы, непосредственно соединенный с портом вывода.

open_system('gm_hdlcoder_constant_subsystem_boundary.slx') set_param('gm_hdlcoder_constant_subsystem_boundary','SimulationCommand','Update') open_system('gm_hdlcoder_constant_subsystem_boundary/DUT/Constant_subsys2')

Идентификатор руководства

1.2.5

Серьезность

Рекомендуется

Описание

Чтобы создать параметризованный код HDL для блоков усиления и константы:

Подсистема, содержащая блоки усиления и константы, должна быть маскированной подсистемой. Блоки усиления и константы используют эти значения параметров маски. Параметры маски подсистемы определяются в диалоговом окне Редактор масок (Mask Editor).

Подсистема, содержащая блоки усиления и константы, должна быть атомной подсистемой. Чтобы сделать подсистему атомной подсистемой, щелкните ее правой кнопкой мыши и выберите Обработать как атомную единицу.

Включить параметр Генерировать параметризованный код HDL из маскированной подсистемы (Generate parameterized HDL code from masked subsystem) в диалоговом окне Параметры конфигурации (Configuration Parameters) MaskParameterAsGeneric кому on в командной строке с использованием makehdl или hdlset_param.

Например, откройте модель. hdlcoder_masked_subsystems. Top Подсистема содержит две подсистемы с атомной маскировкой MASKSUB и MASKSUB1 , которые аналогичны, но для маскированных значений параметров.

load_system('hdlcoder_masked_subsystems') set_param('hdlcoder_masked_subsystems', 'SimulationCommand', 'Update') open_system('hdlcoder_masked_subsystems/TOP')

Модель имеет MaskParameterAsGeneric параметр включен. Этот параметр соответствует параметризованному коду HDL из параметра маскированной подсистемы, который включен в командной строке.

hdlsaveparams('hdlcoder_masked_subsystems')

%% Set Model 'hdlcoder_masked_subsystems' HDL parameters

hdlset_param('hdlcoder_masked_subsystems', 'HDLSubsystem', 'hdlcoder_masked_subsystems/TOP');

hdlset_param('hdlcoder_masked_subsystems', 'MaskParameterAsGeneric', 'on');

Создание кода VHDL для Top Подсистема, выполните следующую команду:

makehdl('hdlcoder_masked_subsystems/TOP')

В созданном коде показано, что HDL Coder™ генерирует один файл HDL. MaskedSub с различными маскированными параметрами, сопоставленными с универсальными портами.

-- -------------------------------------------------------------

--

-- File Name: hdlsrc\hdlcoder_masked_subsystems\TOP.vhd

-- Created: 2018-10-08 13:30:02

--

-- Generated by MATLAB 9.6 and HDL Coder 3.13

--

--

-- -------------------------------------------------------------

--

--

ARCHITECTURE rtl OF TOP IS

-- Component Declarations

COMPONENT MASKSUB

GENERIC( m : integer;

b : integer

);

PORT( x : IN std_logic_vector(7 DOWNTO 0); -- uint8

y : OUT std_logic_vector(16 DOWNTO 0) -- ufix17

);

END COMPONENT;

-- Component Configuration Statements

FOR ALL : MASKSUB

USE ENTITY work.MASKSUB(rtl);

-- Signals

SIGNAL MASKSUB_out1 : std_logic_vector(16 DOWNTO 0); -- ufix17

SIGNAL MASKSUB1_out1 : std_logic_vector(16 DOWNTO 0); -- ufix17

BEGIN

u_MASKSUB : MASKSUB

GENERIC MAP( m => 5,

b => 2

)

PORT MAP( x => In1, -- uint8

y => MASKSUB_out1 -- ufix17

);

u_MASKSUB1 : MASKSUB

GENERIC MAP( m => 6,

b => 4

)

PORT MAP( x => In1, -- uint8

y => MASKSUB1_out1 -- ufix17

);

Out1 <= MASKSUB_out1;

Out2 <= MASKSUB1_out1;

END rtl;

1.2.6

Обязательный

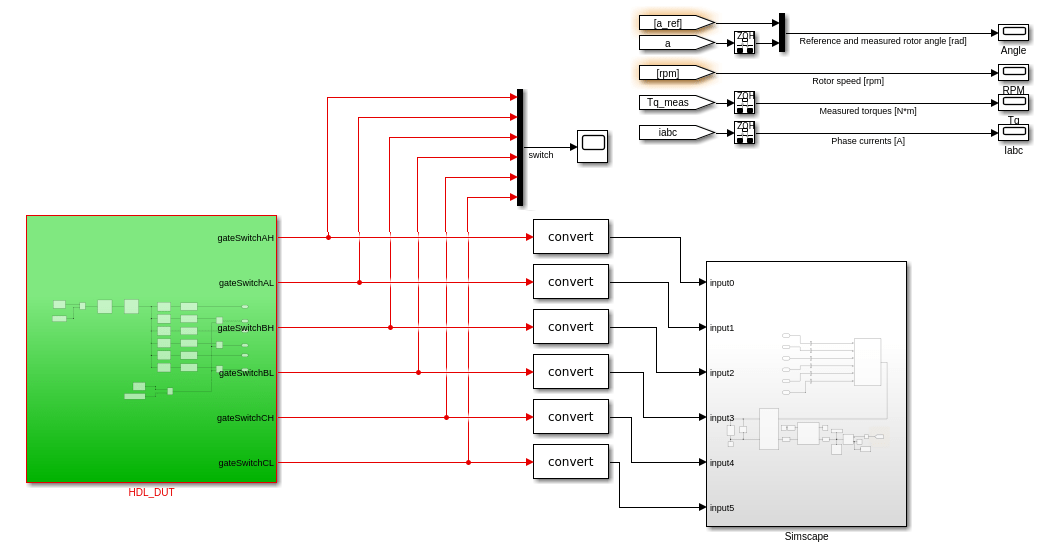

Во избежание ошибок при формировании тестового стенда HDL, физические сигнальные линии, которые присутствуют на том же уровне, что и подсистема DUT, должны быть размещены внутри блока подсистемы. Например, рассмотрим модель Simulink ®, которая имеет физические сигнальные линии вне подсистемы DUT ,HDL_DUT.

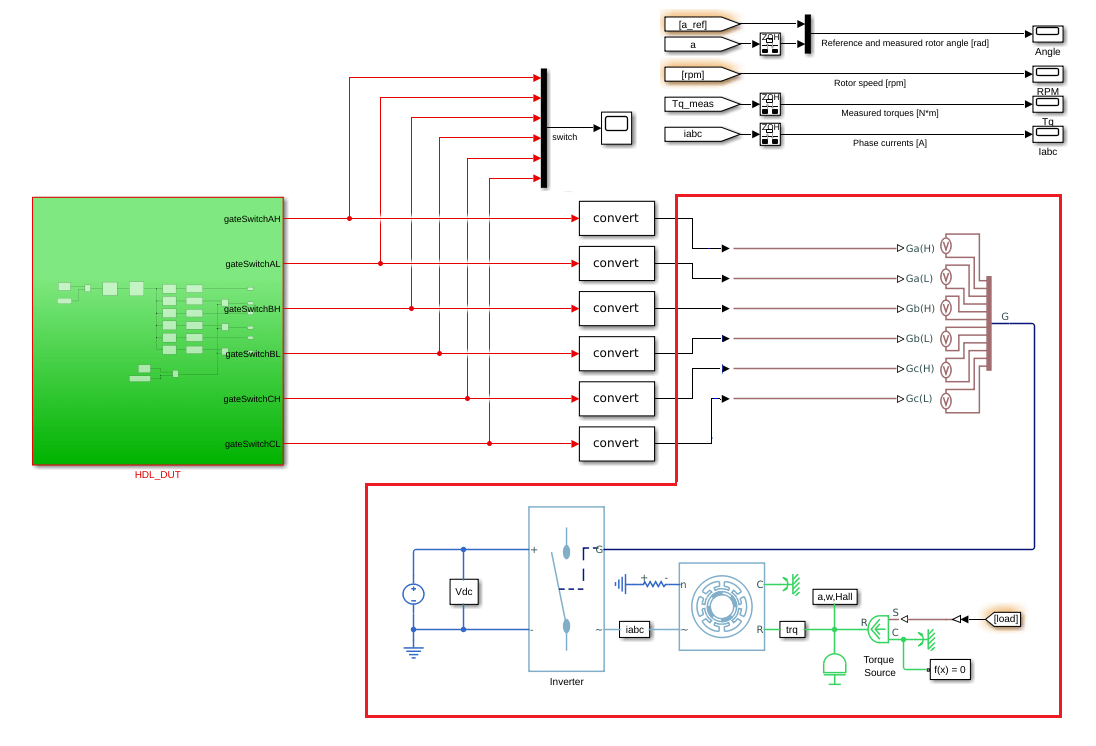

Разместите физические сигнальные линии и связанные с ними блоки, выделенные внутри блока подсистемы. Затем можно создать код HDL и тестовый стенд для подсистемы DUT.