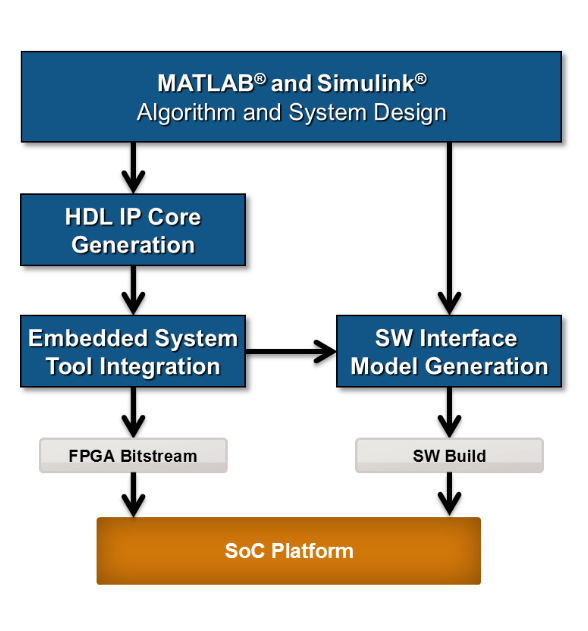

Рабочий процесс совместного проектирования аппаратного и программного обеспечения HDL Coder™ помогает автоматизировать развертывание проекта MATLAB ® и Simulink ® на платформе Zynq ® -7000 или платформе Intel ® SoC. Можно изучить наилучшие способы секционирования и развертывания конструкции, выполнив итерацию в следующем рабочем процессе.

MATLAB и Simulink Algorithm and System Design: Вы начинаете с реализации своего дизайна в MATLAB или Simulink. Когда поведение конструкции соответствует вашим требованиям, решите, как разделять конструкцию: какие детали вы хотите запускать на оборудовании и какие вы хотите запускать во встроенном ПО.

Часть конструкции, которую требуется запустить в аппаратном обеспечении, должна использовать синтаксис MATLAB или блоки Simulink, которые поддерживаются и настраиваются для создания кода HDL. См.:

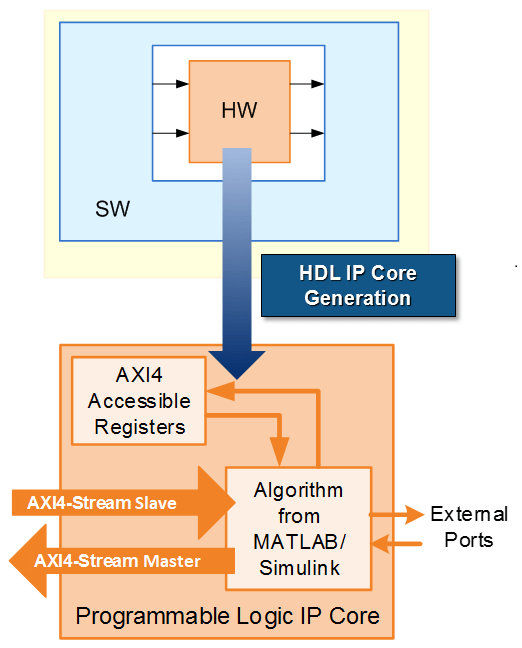

Поколение IP-ядра HDL: заключите аппаратную часть конструкции в атомарный блок подсистемы или функцию MATLAB и используйте помощник по рабочему процессу HDL для определения и генерации IP-ядра HDL.

На следующей схеме показана конструкция, разделенная на аппаратную часть оранжевого цвета и программную часть синего цвета. Генерация ядра IP HDL создает ядро IP из аппаратной части модели. Ядро IP включает в себя аппаратные компоненты интерфейса, такие как доступные AXI4 регистры, интерфейсы AXI4 или AXI4-Lite, интерфейсы AXI4-Stream или AXI4-Stream Video, интерфейсы AXI4 Master и внешние порты.

Интеграция с встроенными системными инструментами: В рамках процесса создания IP-ядра HDL Workflow Advisor вы вставляете созданное IP-ядро в эталонную конструкцию и генерируете битовый поток FPGA для оборудования SoC.

Эталонный проект представляет собой предварительно определенный проект интеграции встроенной системы. Он содержит все элементы, необходимые ПО Intel или Xilinx ® для развертывания вашего проекта на платформе SoC, за исключением пользовательского IP-ядра и встроенного ПО, которое вы создаете.

Следующая диаграмма иллюстрирует взаимосвязь между эталонной конструкцией зеленого цвета и сгенерированным ядром IP оранжевого цвета.

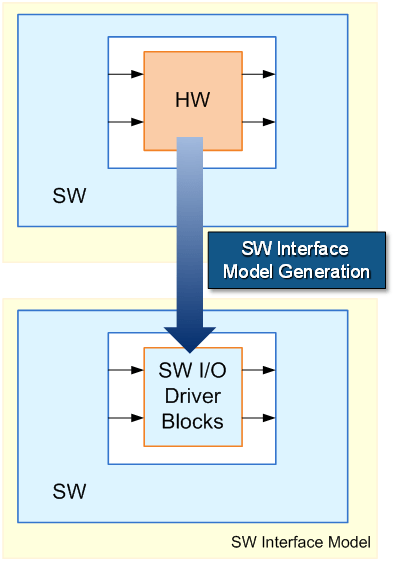

SW Interface Generation (требуется лицензия Simulink и Embedded Coder ®): В методе HDL Workflow Advisor после создания IP-ядра и его вставки в эталонный проект можно дополнительно создать модель программного интерфейса и сценарий программного интерфейса. Модель программного интерфейса - это исходная модель с блоками драйверов AXI, заменяющими аппаратную часть. Сценарий представляет собой файл MATLAB, который создается на основе параметров эталонного дизайна и таблицы интерфейса целевой платформы. Он содержит команды, позволяющие подключаться к целевому оборудованию, а также записывать данные в сгенерированное ядро IP или считывать из него с помощью блоков драйверов AXI.

Если у вас есть лицензия Embedded Coder, вы можете автоматически генерировать модель программного интерфейса и скрипт, создавать из него встроенный код, а также создавать и запускать исполняемый файл в ядре Linux ® на процессоре ARM ®. Созданное встроенное программное обеспечение включает в себя код драйвера AXI, сгенерированный из блоков драйвера AXI, который управляет ядром IP HDL.

Если у вас нет лицензии Embedded Coder или Simulink, вы можете написать встроенное программное обеспечение и вручную построить его для процессора ARM. См. раздел Создание скрипта программного интерфейса для проверки и быстрого прототипа IP-ядра HDL

На следующей диаграмме показано различие между исходной моделью и моделью интерфейса программного обеспечения.

SoC Platform and External Mode PIL: с помощью HDL Workflow Advisor вы программируете битовый поток FPGA на платформу SoC. Затем можно запустить модель интерфейса программного обеспечения во внешнем режиме или режиме процессора в цикле (PIL) для тестирования развернутой конструкции.

Если развернутая конструкция не соответствует требованиям к конструкции, можно повторить рабочий процесс с измененной моделью или другим разделом аппаратного и программного обеспечения.