При запуске рабочего процесса совместного проектирования аппаратного и программного обеспечения для платформ SoC создается IP-ядро HDL для алгоритма DUT, а затем выполняется интеграция IP-ядра в эталонный проект. См. раздел Рабочий процесс совместного проектирования аппаратного и программного обеспечения для платформ SoC.

Для быстрого создания прототипа и тестирования IP-ядра HDL на целевом оборудовании можно создать сценарий программного интерфейса. Сценарий содержит порты DUT и информацию о сопоставлении интерфейсов, которые Coder™ HDL использует для создания драйверов AXI и доступа к ядру IP HDL.

Целевая платформа, например, ZedBoard, на которой требуется развернуть модель интерфейса программного обеспечения.

Последняя версия стороннего средства синтеза, например, Xilinx ® Vivado ®. См. раздел Языковая поддержка HDL и поддерживаемые сторонние инструменты и оборудование. В сессии MATLAB ® задайте путь к установленному инструменту синтеза с помощью hdlsetuptoolpath функция.

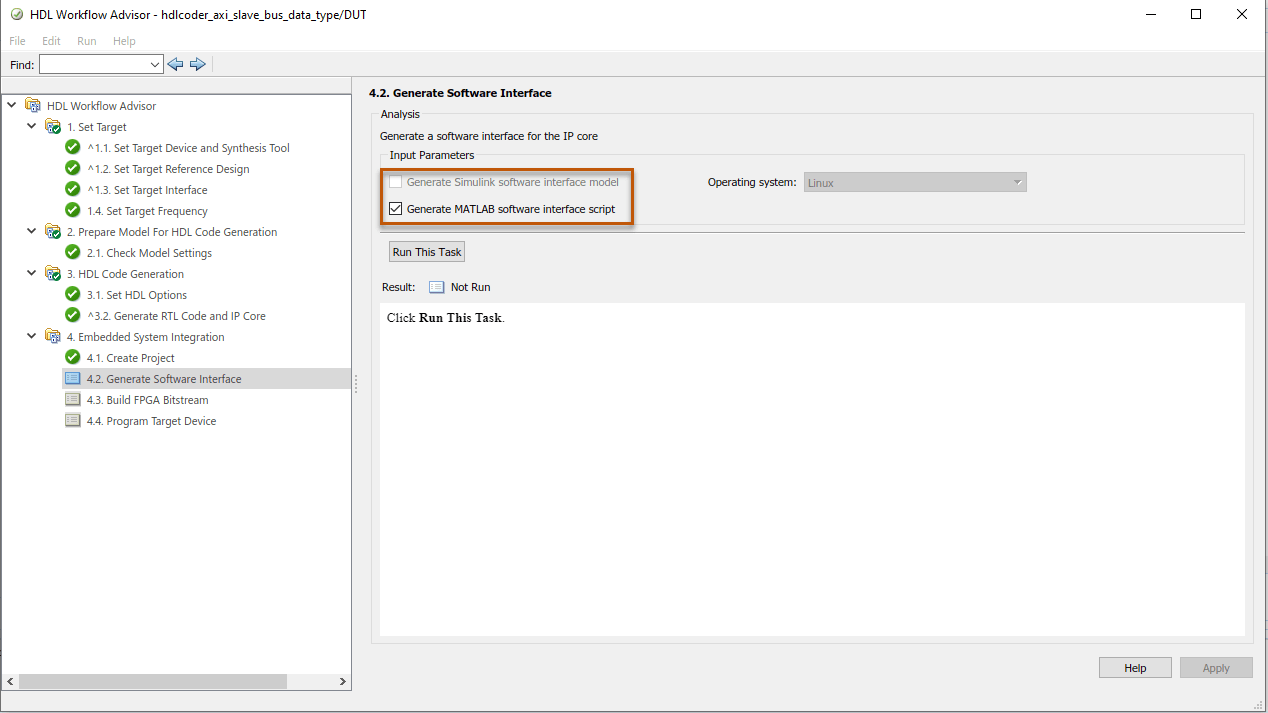

При выполнении рабочего процесса генерации IP Core можно создать сценарий и модель интерфейса программного обеспечения из пользовательского интерфейса помощника по рабочим процессам HDL или в командной строке.

В пользовательском интерфейсе в задаче Интеграция встроенной системы > Создание интерфейса программного обеспечения установите флажок Генерировать сценарий интерфейса программного обеспечения.

При запуске рабочего процесса создания IP-ядра для задачи «Генерировать программный интерфейс» и установке флажка «Генерировать сценарий программного интерфейса MATLAB» создаются два файла MATLAB:

gs_modelName_setup.m, который представляет собой сценарий установки, добавляющий AXI4 подчиненный и AXI4-Stream интерфейсы. Сценарий также содержит объекты порта DUT, которые имеют имя порта, направление, тип данных и информацию о сопоставлении интерфейса. Затем сценарий сопоставляет порты DUT с соответствующими интерфейсами.

gs_modelName_interface.m, который создает целевой объект, создает экземпляр сценария установки gs_modelName_setup.m, а затем подключается к целевому оборудованию. Затем сценарий посылает команды чтения и записи в сформированное ядро IP HDL.

При использовании автономных плат FPGA невозможно создать модель интерфейса программного обеспечения. Вместо этого можно создать сценарий программного интерфейса и протестировать ядро IP с помощью драйвера MATLAB AXI Master.

В задаче Задать целевое ссылочное проектирование (Set Target Reference Design) установите для команды Вставить JTAG MATLAB (Insert JTAG MATLAB) значение Мастер AXI (AXI Master) значение on Запустите рабочий процесс для задачи «Создать программный интерфейс».

В задаче «Создать программный интерфейс» установите флажок «Создать сценарий программного интерфейса» и запустите эту задачу.

В командной строке экспортируйте параметры помощника по рабочим процессам HDL в сценарий, а затем используйте эти свойства с объектом «Конфигурация рабочего процесса». Этот сценарий определяет выполнение задачи программного интерфейса путем создания модели и сценария. Если пропустить задачу, установив для параметра RunTaskGenerateGroupInterface значение false, модель и сценарий не будут созданы. См. раздел Настройка и запуск рабочего процесса создания ядра IP со сценарием.

% Export Workflow Configuration Script % ... %% Load the Model load_system('hdlcoder_led_blinking'); %% Model HDL Parameters % Set Model HDL parameters % ... hdlset_param('hdlcoder_led_blinking', 'SynthesisTool', 'Xilinx Vivado'); hdlset_param('hdlcoder_led_blinking', 'Workflow', 'IP Core Generation'); % ... % Set Workflow tasks to run hWC.RunTaskGenerateSoftwareInterface = true; hWC.GenerateSoftwareInterfaceModel = true; hWC.GenerateSoftwareInterfaceScript = true; % ... %% Run the workflow hdlcoder.runWorkflow('hdlcoder_led_blinking/led_counter', hWC);

Для быстрого создания прототипов и тестирования основных функций HDL IP используйте сценарий программного интерфейса. Сценарий представляет собой файл MATLAB, который создается на основе параметров эталонного дизайна и таблицы интерфейса целевой платформы. Он содержит команды, позволяющие подключаться к целевому оборудованию, а также выполнять запись или считывание из созданного IP-ядра из MATLAB. Для автономных плат FPGA используйте сгенерированный скрипт интерфейса программного обеспечения для проверки основных функций HDL IP с помощью MATLAB AXI Master.

Сценарий интерфейса программного обеспечения имеет то же имя, что и исходная модель с префиксом gs_ и постфикс _interface. Сценарий создает экземпляр функции установки, которая создается при включении генерации сценария интерфейса программного обеспечения. Например, этот код показывает функцию настройки, созданную для модели hdlcoder_sfir_fixed_stream.slx, с предварительно заданными настройками эталонного дизайна и таблицы интерфейса целевой платформы. Функция установки содержит команды для AXI4 подчиненного и AXI4-Stream интерфейсов, используемых кодером HDL для управления портами DUT в сгенерированном ядре IP HDL, которые сопоставляются с соответствующими интерфейсами.

function gs_hdlcoder_sfir_fixed_stream_setup(hFPGA) %-------------------------------------------------------------------------- % Software Interface Script Setup % % Generated with MATLAB 9.10 (R2021a) at 09:13:05 on 10/07/2020. % This function was created for the IP Core generated from design 'hdlcoder_sfir_fixed_stream'. % % Run this function on an "fpga" object to configure it with % the same interfaces as the generated IP core. %-------------------------------------------------------------------------- %% AXI4-Lite addAXI4SlaveInterface(hFPGA, ... "InterfaceID", "AXI4-Lite", ... "BaseAddress", 0xA0000000, ... "AddressRange", 0x10000); hPort_h_in1 = hdlcoder.DUTPort("h_in1", ... "Direction", "IN", ... "DataType", numerictype(1,16,10), ... "Dimension", [1 1], ... "IOInterface", "AXI4-Lite", ... "IOInterfaceMapping", "0x100"); hPort_h_in2 = hdlcoder.DUTPort("h_in2", ... "Direction", "IN", ... "DataType", numerictype(1,16,10), ... "Dimension", [1 1], ... "IOInterface", "AXI4-Lite", ... "IOInterfaceMapping", "0x104"); hPort_h_in3 = hdlcoder.DUTPort("h_in3", ... "Direction", "IN", ... "DataType", numerictype(1,16,10), ... "Dimension", [1 1], ... "IOInterface", "AXI4-Lite", ... "IOInterfaceMapping", "0x108"); hPort_h_in4 = hdlcoder.DUTPort("h_in4", ... "Direction", "IN", ... "DataType", numerictype(1,16,10), ... "Dimension", [1 1], ... "IOInterface", "AXI4-Lite", ... "IOInterfaceMapping", "0x10C"); mapPort(hFPGA, [hPort_h_in1, hPort_h_in2, hPort_h_in3, hPort_h_in4]); %% AXI4-Stream addAXI4StreamInterface(hFPGA, ... "InterfaceID", "AXI4-Stream", ... "WriteEnable", true, ... "WriteFrameLength", 1024, ... "ReadEnable", true, ... "ReadFrameLength", 1024); hPort_x_in_data = hdlcoder.DUTPort("x_in_data", ... "Direction", "IN", ... "DataType", numerictype(1,16,10), ... "Dimension", [1 1], ... "IOInterface", "AXI4-Stream"); hPort_y_out_data = hdlcoder.DUTPort("y_out_data", ... "Direction", "OUT", ... "DataType", numerictype(1,32,20), ... "Dimension", [1 1], ... "IOInterface", "AXI4-Stream"); mapPort(hFPGA, [hPort_x_in_data, hPort_y_out_data]); end

Это пример функции установки для модели с шиной, сопоставленной с AXI4 подчиненным интерфейсом. Как показано в сценарии, элементы шины представлены в виде подпортов hdlcoder.DUTPort объекты.

function gs_AXI4SlaveMultipleBus_setup(hFPGA) %-------------------------------------------------------------------------- % Software Interface Script Setup % % Generated with MATLAB 9.10 (R2021a) at 16:20:32 on 16/11/2020. % This function was created for the IP Core generated from design 'AXI4SlaveMultipleBus'. % % Run this function on an "fpga" object to configure it with the same interfaces as the generated IP core. %-------------------------------------------------------------------------- %% AXI4 addAXI4SlaveInterface(hFPGA, ... "InterfaceID", "AXI4", ... "BaseAddress", 0x400D0000, ... "AddressRange", 0x10000); hPort_bus1_in_scalar_in1 = hdlcoder.DUTPort("scalar_in1", ... "Direction", "IN", ... "DataType", numerictype('single'), ... "Dimension", [1 1], ... "IOInterface", "AXI4", ... "IOInterfaceMapping", "0x100"); hPort_bus1_in_scalar_in2 = hdlcoder.DUTPort("scalar_in2", ... "Direction", "IN", ... "DataType", numerictype(1,8,0), ... "Dimension", [1 1], ... "IOInterface", "AXI4", ... "IOInterfaceMapping", "0x104"); hPort_bus1_in_scalar_in3 = hdlcoder.DUTPort("scalar_in3", ... "Direction", "IN", ... "DataType", numerictype(1,32,0), ... "Dimension", [1 1], ... "IOInterface", "AXI4", ... "IOInterfaceMapping", "0x108"); hPort_bus1_in_scalar_in4 = hdlcoder.DUTPort("scalar_in4", ... "Direction", "IN", ... "DataType", numerictype(1,16,10), ... "Dimension", [1 1], ... "IOInterface", "AXI4", ... "IOInterfaceMapping", "0x10C"); hPort_bus1_in_vector_in = hdlcoder.DUTPort("vector_in", ... "Direction", "IN", ... "DataType", numerictype(0,32,0), ... "Dimension", [1 2], ... "IOInterface", "AXI4", ... "IOInterfaceMapping", "0x110"); hPort_bus1_in = hdlcoder.DUTPort("bus1_in", ... "Direction", "IN", ... "DataType", "Bus", ... "Dimension", [1 1], ... "IOInterface", "AXI4", ... "SubPorts", [hPort_bus1_in_scalar_in1, hPort_bus1_in_scalar_in2, hPort_bus1_in_scalar_in3, hPort_bus1_in_scalar_in4, hPort_bus1_in_vector_in]);

Сценарий программного интерфейса создает экземпляр этой функции установки для подключения к целевому объекту и отправки команд чтения или записи. Можно раскомментировать и отправлять значимые данные, используя входные данные DUT в исходной модели. После взаимодействия с аппаратным обеспечением сценарий отключается от аппаратного ресурса, связанного с fpga объект.

%-------------------------------------------------------------------------- % Software Interface Script % % Generated with MATLAB 9.10 (R2020b) at 09:13:10 on 10/07/2020. % This script was created for the IP Core generated from design 'hdlcoder_sfir_fixed_stream'. % % Use this script to access DUT ports in the design mapped to compatible IP core interfaces. % You can write to input ports in the design and read from output ports directly from MATLAB. % % To write to input ports, use the "writePort" command and specify port name and input data. % The input data will be cast to the DUT port's data type before writing. % % To read from output ports, use the "readPort" command and specify the port name. % The output data will be returned with the same data type as the DUT port. % % Use the "release" command to release MATLAB's control of the hardware resources. %-------------------------------------------------------------------------- %% Create fpga object hFPGA = fpga("Xilinx"); %% Setup fpga object % This function configures "fpga" object with same interfaces as the generated IP core gs_hdlcoder_sfir_fixed_stream_setup(hFPGA); %% Write/read DUT ports % Uncomment the following lines to write/read DUT ports in the generated IP Core. % Update the example data in the write commands with meaningful data to write to the DUT. %% AXI4-Lite writePort(hFPGA, "h_in1", zeros([1 1])); writePort(hFPGA, "h_in2", zeros([1 1])); writePort(hFPGA, "h_in3", zeros([1 1])); writePort(hFPGA, "h_in4", zeros([1 1])); %% AXI4-Stream writePort(hFPGA, "x_in_data", zeros([1 1024])); data_y_out_data = readPort(hFPGA, "y_out_data"); %% Release hardware resources release(hFPGA)

См. Проект прототипа FPGA на оборудовании с динамическими данными с помощью команд MATLAB

Это пример сценария программного интерфейса для чтения и записи данных для моделей, которые имеют типы данных шины, сопоставленные с AXI4 подчиненными интерфейсами.

Для записи в порт шины можно выполнить одно из следующих действий:

Запись в отдельные подпорты путем указания полного имени подпорта, например bus1_in.scalar_in1.

Выполните запись на всю шину, указав имя верхнего порта, например bus1_in. Передайте данные для записи в виде структуры, имена полей которой соответствуют именам подпортов. Не все имена подчиненных портов должны быть частью структуры. Подпорты без соответствующих полей структуры пропускаются при записи в порт.

Для чтения из порта шины можно выполнить одно из следующих действий:

Прочтите отдельный подпорт, указав полное имя подпорта, например bus1_out.scalar.in1.

Прочтите весь порт шины, указав имя верхнего порта, например bus1_out.

%-------------------------------------------------------------------------- % Software Interface Script % % Generated with MATLAB 9.10 (R2021a) at 16:20:33 on 16/11/2020. % This script was created for the IP Core generated from design 'AXI4SlaveMultipleBus'. % % Use this script to access DUT ports in the design that were mapped to compatible IP core interfaces. % You can write to input ports in the design and read from output ports directly from MATLAB. % To write to input ports, use the "writePort" command and specify the port name and input data. The input data will be cast to the DUT port's data type before writing. % To read from output ports, use the "readPort" command and specify the port name. The output data will be returned with the same data type as the DUT port. % Use the "release" command to release MATLAB's control of the hardware resources. %-------------------------------------------------------------------------- %% Create fpga object hFPGA = fpga("Xilinx"); %% Setup fpga object % This function configures the "fpga" object with the same interfaces as the generated IP core gs_AXI4SlaveMultipleBus_setup(hFPGA); %% Write/read DUT ports % Uncomment the following lines to write/read DUT ports in the generated IP Core. % Update the example data in the write commands with meaningful data to write to the DUT. %% AXI4 % There are two ways to write a DUT bus ports % (1). Prepare a struct value and write it to the whole bus port. writePort(hFPGA, "bus1_in", struct()); % (2). Prepare a value for each member of the bus and write it individually. writePort(hFPGA, "bus1_in.scalar_in1", zeros([1 1])); writePort(hFPGA, "bus1_in.scalar_in2", zeros([1 1])); writePort(hFPGA, "bus1_in.scalar_in3", zeros([1 1])); writePort(hFPGA, "bus1_in.scalar_in4", zeros([1 1])); writePort(hFPGA, "bus1_in.vector_in", zeros([1 2]));