Импорт HDL используется для импорта синтезируемого кода HDL в среду моделирования Simulink ®. Импорт HDL анализирует входной файл HDL и генерирует модель Simulink. Модель представляет собой среду блок-схемы, которая визуально представляет код HDL с точки зрения функциональности и поведения. Импортируя код HDL в Simulink, можно проверить функциональность кода HDL, скомпилировав и запустив моделирование модели в среде моделирования на основе модели. Можно также выполнить отладку внутренних сигналов путем регистрации сигналов в качестве контрольных точек.

Генерация кода в оба конца с импортом HDL не рекомендуется. Не используйте импорт HDL для импорта кода HDL, ранее созданного в модели Simulink с помощью программного обеспечения HDL Coder™. Создаваемая модель Simulink обычно находится на более высоком уровне абстракции. Модель, созданная при импорте HDL, может находиться на более низком уровне абстракции. Код HDL, созданный на основе этой модели, может не использоваться для производственного кода.

Чтобы создать производственный код HDL, разработайте алгоритм с помощью блоков Simulink, кода MATLAB ® или диаграмм Stateflow ®. Затем используйте кодер HDL для создания кода.

Чтобы создать модель Simulink, убедитесь, что импортируемый файл HDL:

Не содержит синтаксических ошибок.

Синтезируется.

Использует поддерживаемые конструкции Verilog ® для импорта.

Для импорта кода HDL в окне команд MATLAB выполните команду importhdl функция. Например, для импорта файла Verilog example.v, в командной строке введите:

importhdl('example.v')Конструкции, используемые в коде HDL, могут выводить простые блоки Simulink, такие как блоки Add и Product to RAM, такие как двухскоростная двухпортовая RAM. Примеры, иллюстрирующие различные выводимые модели Simulink, см. в разделе importhdl.

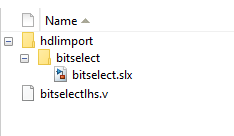

Созданная модель Simulink называется по имени верхнего модуля во входном файле HDL, который вы указываете. Модель сохраняется в hdlimport/TopModule путь относительно текущей рабочей папки. Например, при вводе файла с именем bitselectlhs.v в importhdl функция, которая имеет bitselect в качестве имени верхнего модуля созданная модель Simulink имеет имя bitselect.slxи сохраняется в hdlimport/bitselect путь относительно текущей папки.

При запуске importhdl функция импорта HDL проверяет синтаксис и семантику входного кода HDL. Семантическая проверка для конструкций экземпляра модуля, неиспользуемых портов в определении модуля, списка чувствительности always блок и так далее. При сбое импорта HDL importhdl предоставляет сообщение об ошибке и ссылку на имя файла и номер строки.

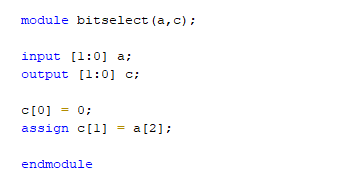

Например, рассмотрим этот код Verilog для bitselect модуль:

При запуске importhdl функция, импорт HDL генерирует сообщение об ошибке:

Parser Error: bitselectlhs.v:6:2: error: Syntax Error near '['..

Сообщение об ошибке указывает на наличие синтаксической ошибки в строке 6. Чтобы устранить эту ошибку, измените синтаксис на инструкцию назначения.

assign c[0] = 0;

Импорт HDL не поддерживает:

Импорт файлов VHDL.

Импорт файлов Verilog из папки только для чтения.

Создание файлов предварительной обработки в файловой системе только для чтения, которые анализируют код HDL, введенный в importhdl функция.

Экземпляры атрибутов и комментарии, которые игнорируются.

(#) значения задержки, такие как#25, которые игнорируются.

Типы данных перечисления.

Более одного тактового сигнала.

Многоскоростные модули.

Экземпляр рекурсивного модуля.

Вывод мультипортового коммутатора с более чем 1024 входные данные. Если указано более 1024 вход в блок многопортового коммутатора, который выводится из кода Verilog, импорт Verilog генерирует ошибку. Ошибка генерируется, поскольку среда моделирования Simulink не поддерживает более 1024 входы для блока.

Обнаружение ПЗУ из кода Verilog.

Импорт файлов HDL, использующих неподдерживаемые конструкции Verilog. См. раздел Поддерживаемые конструкции Verilog для импорта HDL.

Импорт файлов HDL, использующих неподдерживаемые шаблоны моделирования потока данных. См. раздел Неподдерживаемые шаблоны потока данных Verilog.