HDL Coder™ использует IP Core Generation инфраструктура рабочего процесса для создания многоразового IP-ядра HDL для программируемых модулей ввода/вывода Speedgoat Simulink, поддерживающих Xilinx ® Vivado ®. Рабочий процесс создает отчет о ядре IP, в котором отображается конфигурация целевого интерфейса и заданные параметры генератора кода. Ядро IP можно интегрировать в более крупную конструкцию, добавив его во встроенную среду системной интеграции. См. раздел Пользовательское поколение ядра IP.

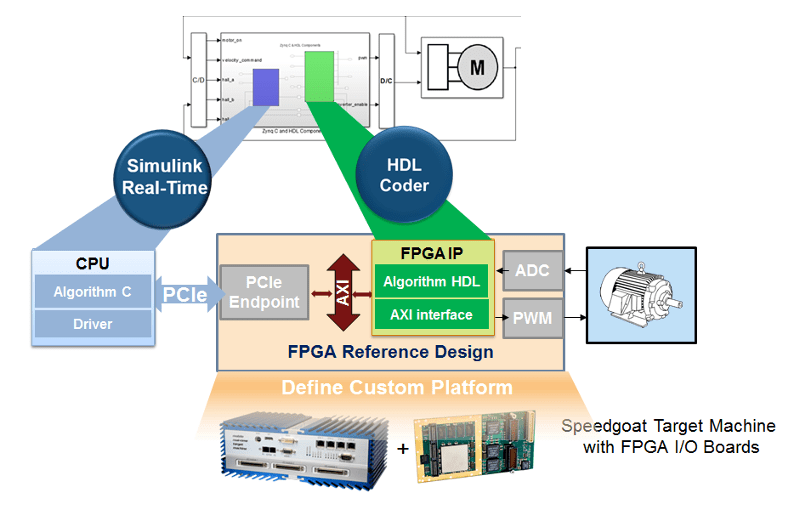

На этом рисунке показано, как программное обеспечение генерирует ядро IP с интерфейсом AXI и интегрирует ядро IP в эталонную конструкцию FPGA.

Чтобы узнать о модулях ввода/вывода, которые поддерживает кодер HDL с помощью Simulink Real-Time FPGA I/O см. раздел Поддержка Speedgoat FPGA с помощью помощника по рабочим процессам HDL.

Этот рабочий процесс имеет следующие ключевые функции:

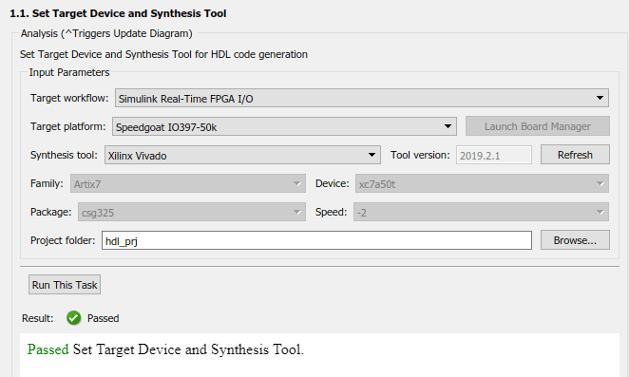

Использует Xilinx Vivado в качестве инструмента синтеза.

Создает многоразовое и совместно используемое ядро IP. Ядро IP упаковывает код RTL, файл заголовка C и файлы определения ядра IP.

Создает проект для интеграции IP-ядра в эталонный проект Speedgoat.

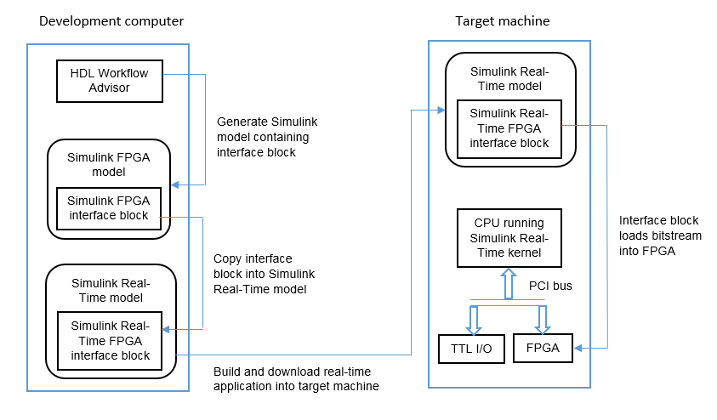

Генерирует битовый поток FPGA и загружает его на целевое оборудование.

После создания битового потока FPGA рабочий процесс создает модель Simulink ® Real-Time™. Модель представляет собой модель интерфейсной подсистемы, которая содержит блоки для программирования FPGA и обмена данными с модулем ввода-вывода через PCI-шину во время выполнения в реальном времени .

IP Core Generation рабочий процесс не поддерживает:

Для архитектуры ОЗУ установлено значение Generic RAM without clock enable.

Использование различных часов для ядра IP и интерфейса AXI. IPCore_Clk и AXILite_ACLK должна быть синхронной и подключенной к одному и тому же источнику синхросигналов. IPCore_RESETN и AXILite_ARESETN должен быть подключен к тому же источнику сброса. См. раздел Синхронизация сигнала глобального сброса с доменом тактовой синхронизации ядра IP.