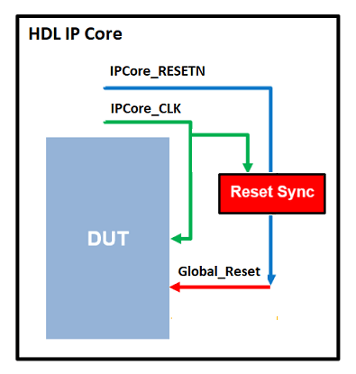

Ядро IP HDL DUT и логику Декодера Адреса в обертке интерфейса AXI4 Slave IP ядра HDL ведет глобальный сигнал сброса. Если Вы производите IP ядро HDL без каких-либо рабских интерфейсов AXI4, HDL Coder™ не производит рабскую обертку интерфейса AXI4. Сигнал глобального сброса становится таким же, как сигнал сброса ядра IP, и управляет ядром IP HDL для DUT. Сведения о том, как можно создать ядро IP без AXI4 подчиненных интерфейсов, см. в разделе Создание независимого от платы ядра HDL IP из Simulink Model.

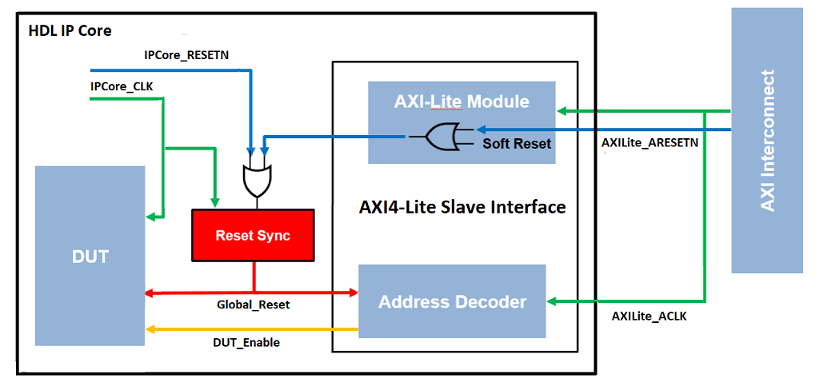

При генерации AXI4 подчиненных интерфейсов в IP-ядре HDL сигнал глобального сброса управляется тремя сигналами сброса: внешним сбросом IP-ядра, сигналом сброса межсоединений AXI и мягким сбросом ядра процессора ARM. В этом случае сигнал глобального сброса управляет ядром IP HDL для DUT и логикой декодера адресов в AXI4 подчиненной оболочке.

IPCore_Clk и AXILite_ACLK должен быть подключен к тому же источнику синхросигналов. IPCore_RESETN и AXILite_ARESETN должен быть подключен к тому же источнику сброса.

Эти сигналы сброса могут быть синхронными или асинхронными. Использование асинхронных сигналов сброса может быть проблематичным и приводить к потенциальным проблемам метастабильности во флипфлопах, когда сброс отменяется в пределах фиксирующего окна часов. Чтобы избежать генерации возможных метастабильных значений при объединении сигналов сброса, кодер HDL автоматически вставляет логику синхронизации сброса, как указано Reset Sync блок. Логика синхронизации сброса синхронизирует сигнал глобального сброса с основной областью синхронизации IP. Эта логика вставляется при открытии помощника по рабочим процессам HDL и выполнении задачи «Генерировать код RTL и ядро IP» IP Core Generation workflow-процесс.

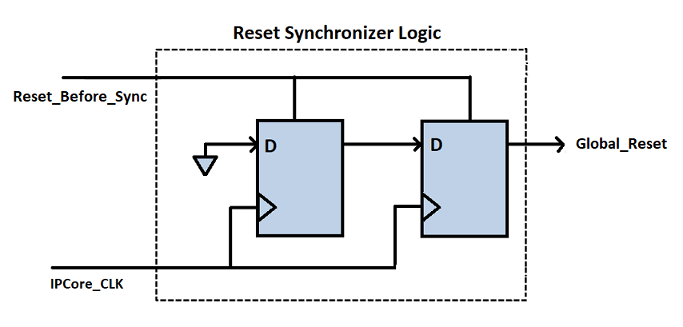

Логика синхронизации сброса содержит два обратных флипфлопа, которые синхронизированы с IPCore_CLK сигнал. Flipflops проверяют, что отмена подтверждения сигнала сброса происходит после двух тактов, когда IPCore_CLK сигнал становится высоким. Эта синхронная отмена утверждения позволяет избежать генерации глобального сигнала сброса, который имеет возможные метастабильные значения.

Логика работает по-разному в зависимости от того, задан ли тип Reset как Synchronous или Asynchronous на модели. Если тип сброса - Asynchronous, логика синхронизации асинхронно устанавливает сигнал сброса и синхронно отменяет сигнал сброса. Например, этот код иллюстрирует сгенерированный код Verilog ® для логики синхронизации сброса при создании ядра IP с асинхронным сбросом.

...

...

reg_reset_pipe_process : PROCESS (clk, reset_in)

BEGIN

IF reset_in = '1' THEN

reset_pipe <= '1';

ELSIF clk'EVENT AND clk = '1' THEN

IF enb = '1' THEN

reset_pipe <= const_0;

END IF;

END IF;

END PROCESS reg_reset_pipe_process;

reg_reset_delay_process : PROCESS (clk, reset_in)

BEGIN

IF reset_in = '1' THEN

reset_out <= '1';

ELSIF clk'EVENT AND clk = '1' THEN

IF enb = '1' THEN

reset_out <= reset_pipe;

END IF;

END IF;

END PROCESS reg_reset_delay_process;

END rtl;

Если тип сброса - Synchronous, логика синхронизации синхронно устанавливает и отменяет сигнал сброса. Например, этот код иллюстрирует сгенерированный код Verilog для логики синхронизации сброса при генерации ядра IP с синхронным сбросом.

...

...

reg_reset_pipe_process : PROCESS (clk)

BEGIN

IF clk'EVENT AND clk = '1' THEN

IF reset_in = '1' THEN

reset_pipe <= '1';

ELSIF enb = '1' THEN

reset_pipe <= const_0;

END IF;

END IF;

END PROCESS reg_reset_pipe_process;

reg_reset_delay_process : PROCESS (clk)

BEGIN

IF clk'EVENT AND clk = '1' THEN

IF reset_in = '1' THEN

reset_out <= '1';

ELSIF enb = '1' THEN

reset_out <= reset_pipe;

END IF;

END IF;

END PROCESS reg_reset_delay_process;

END rtl;