С помощью HDL Workflow Advisor можно создать пользовательское ядро IP из модели или алгоритма. Сгенерированное ядро IP может совместно использоваться и повторно. Вы можете интегрировать его с более крупным дизайном, добавив его в среду интеграции встраиваемых систем, такую как Intel ® Qsys, Xilinx ® EDK или Xilinx IP Integrator.

Чтобы узнать, как создать пользовательское ядро IP, см.:

Можно создать ядро IP:

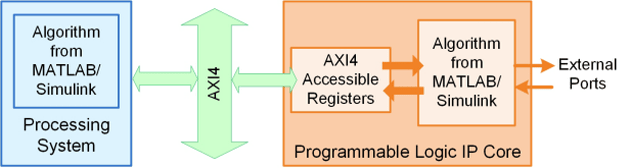

С интерфейсом AXI4 или AXI4-Lite.

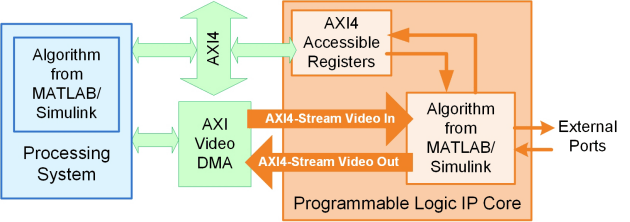

С интерфейсом AXI4 или AXI4-Lite и интерфейсами AXI4-Stream Video.

Без каких-либо AXI4 или AXI4-Lite интерфейсов. Дополнительные сведения см. в разделе Создание независимого от платы ядра HDL IP на основе модели Simulink.

Алгоритм из блока MATLAB/Simulink представляет DUT. HDL Coder™ генерирует остальную часть IP-ядра на основе настроек интерфейса целевой платформы и режима синхронизации процессора/FPGA.

Каждый порт в DUT можно сопоставить с одним из следующих интерфейсов целевой платформы в ядре IP:

AXI4-Lite: Используйте этот подчиненный интерфейс для доступа к регистрам управления или для облегченной передачи данных. Кодер HDL генерирует преобразованные в память регистры и назначает смещения адресов для портов, которые сопоставляются с этим интерфейсом.

AXI4: Используйте этот подчиненный интерфейс для подключения к компонентам, поддерживающим пакетную передачу данных. Кодер HDL генерирует преобразованные в память регистры и назначает смещения адресов для портов, которые сопоставляются с этим интерфейсом.

Примечание

Интерфейсы AXI4 и AXI4-Lite также называются AXI4 подчиненными интерфейсами. В сгенерированном IP-ядре HDL можно использовать либо AXI4, либо AXI4-Lite интерфейс, но не оба интерфейса.

AXI4-Stream Video: Используйте этот интерфейс для отправки или получения 32-разрядного скалярного потока видеоданных.

Внешние порты: используйте внешние порты для подключения к внешним контактам ввода-вывода FPGA или к другим ядрам IP с внешними портами.

FPGA Data Capture - JTAG: Используйте FPGA Data Capture по интерфейсу JTAG для наблюдения сигналов контрольных точек и сигналов на выходных портах DUT, пока ваша конструкция работает на FPGA. Пример маркировки внутренних сигналов в качестве контрольных точек см. в разделе Отладка ядра IP с помощью функции захвата данных FPGA. Дополнительные сведения о захвате данных см. в разделе Рабочий процесс захвата данных (проверка HDL).

Примечание

Для использования этого интерфейса необходимо загрузить пакет аппаратной поддержки для платы FPGA. См. раздел Загрузка пакета поддержки платы FPGA (HDL Verifier).

Дополнительные сведения о протоколах AXI4, AXI4-Lite и AXI4-Stream Video см. в документации по целевому оборудованию.

Кодер HDL генерирует логику синхронизации в ядре IP на основе выбранного режима синхронизации процессора/FPGA.

При создании пользовательского IP-ядра доступны следующие опции синхронизации процессора/FPGA:

Free running (по умолчанию)

Coprocessing – blocking

Дополнительные сведения о режимах синхронизации процессора/FPGA см. в разделе Синхронизация процессора и FPGA.

После создания пользовательского IP-ядра файлы IP-ядра находятся в ipcore в папке проекта. В помощнике по рабочим процессам HDL можно просмотреть имя основной IP-папки в поле основной IP-папки окна Создание кода HDL (HDL Code Generate) > Создать код RTL (Generate RTL Code) и задача Ядро IP (IP Core).

Основная IP-папка содержит следующие сгенерированные файлы:

Файлы определения IP-ядра.

Исходные файлы HDL (.vhd или .v).

Файл заголовка C с картой адресов регистров.

(Необязательно) HTML-отчет с инструкциями по использованию ядра и интеграции ядра IP в проект встраиваемой системы.

IP Core Generation рабочий процесс не поддерживает:

Для архитектуры ОЗУ установлено значение Generic RAM without clock enable.

Использование различных часов для ядра IP и интерфейса AXI. IPCore_Clk и AXILite_ACLK должна быть синхронной и подключенной к одному и тому же источнику синхросигналов. IPCore_RESETN и AXILite_ARESETN должен быть подключен к тому же источнику сброса. См. раздел Синхронизация сигнала глобального сброса с доменом тактовой синхронизации ядра IP.