Настройте рабочую папку, доступную для записи, за пределами установочной папки MATLAB ® для хранения файлов, которые будут создаваться по завершении учебной работы. В инструкциях по обучению предполагается, что создается папкаhdlfilter_tutorials на приводе C.

В этом учебном пособии приведены инструкции по проектированию фильтра IIR, созданию кода Verilog для фильтра и проверке кода Verilog с помощью созданного тестового стенда.

В этом разделе описывается процедура проектирования и создания фильтра для фильтра IIR. В этом разделе предполагается, что пользователь знаком с интерфейсом пользователя MATLAB и конструктором фильтров.

Запустите программное обеспечение MATLAB.

Установите текущую папку в папку, созданную в разделе «Создание папки для файлов учебного пособия».

Запустите конструктор фильтров, введя filterDesigner в окне команд MATLAB. Откроется диалоговое окно Фильтровать инструмент проектирования и анализа (Filter Design & Analysis Tool).

В диалоговом окне «Инструмент проектирования и анализа фильтров» задайте следующие параметры фильтра:

| Выбор | Стоимость |

|---|---|

| Тип ответа | Highpass |

| Метод проектирования | IIR Butterworth |

| Порядок фильтрации |

|

| Частотные характеристики | Единицы измерения: Fs: Fc: |

Щелкните Фильтр проектирования (Design Filter). Конструктор фильтров создает фильтр для указанной конструкции. По завершении задачи в строке состояния конструктора фильтров появится следующее сообщение.

Designing Filter... Done

Дополнительные сведения о проектировании фильтров с помощью конструктора фильтров см. в разделе Использование конструктора фильтров с программным обеспечением DSP System Toolbox.

Следует квантовать фильтры для генерации кода HDL. Чтобы квантовать фильтр,

Откройте конструкцию фильтра IIR, созданную в окне «Проектирование фильтра IIR» в конструкторе фильтров, если она еще не открыта.

Нажмите кнопку «Задать параметры квантования![]() » на левой панели инструментов. Конструктор фильтров отображает арифметический список фильтров в нижней половине диалогового окна.

» на левой панели инструментов. Конструктор фильтров отображает арифметический список фильтров в нижней половине диалогового окна.

Выбрать Fixed-point из списка. Конструктор фильтров отображает первую из трех панелей с вкладками в диалоговом окне.

Используйте опции квантования для проверки влияния различных настроек на производительность и точность квантованного фильтра.

Выберите вкладку Фильтровать внутренние элементы (Filter Internals) и установите режим округления в значение Floor и режим переполнения для Saturate.

Нажмите кнопку «Применить». Квантованный фильтр появляется следующим образом.

Дополнительные сведения о квантовании фильтров с помощью конструктора фильтров см. в разделе Использование конструктора фильтров с программным обеспечением DSP System Toolbox.

После квантования фильтра можно настроить параметры кодера и создать код VHDL. В этом разделе описывается запуск пользовательского интерфейса HDL Coder™ проектирования фильтров, настройка параметров и создание кода VHDL и тестового стенда для IIR-фильтра, который был разработан и квантован при проектировании IIR-фильтра в Filter Designer и квантовании IIR-фильтра.

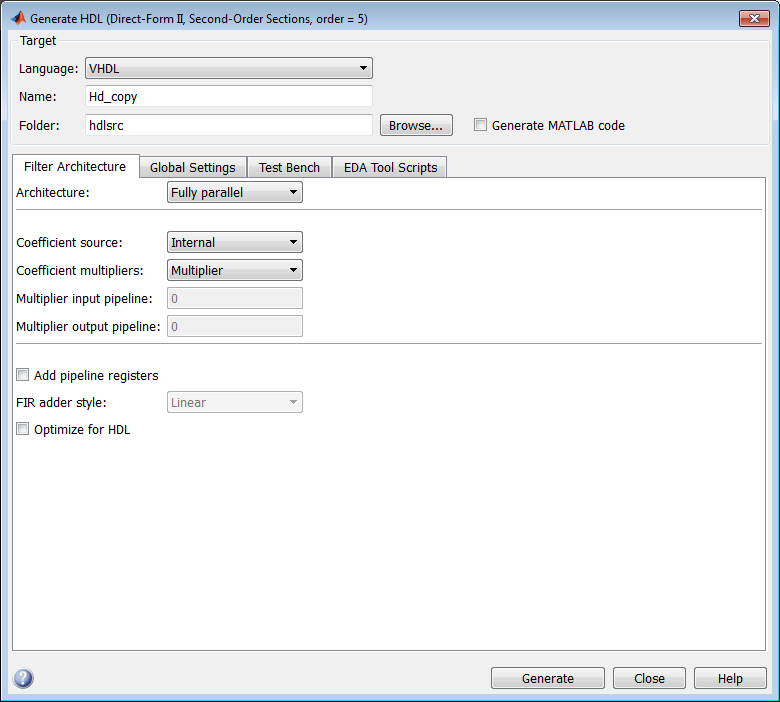

Запустите пользовательский интерфейс кодера HDL проекта фильтра, выбрав «Цели» > «Создать HDL» в диалоговом окне «Конструктор фильтров». Конструктор фильтров отображает диалоговое окно Генерировать ЛПВП (Generate HDL).

В текстовом поле «Имя» на панели «Цель» введите iir. Этот параметр задает имя объекта VHDL и файла, содержащего код VHDL для фильтра.

Выберите вкладку Глобальные параметры пользовательского интерфейса. Затем выберите вкладку Общие в разделе Дополнительные настройки.

В текстовом поле Комментарий в заголовке введите Tutorial - IIR Filter. Кодер добавляет комментарий к концу блока комментариев заголовка в каждом созданном файле.

Выберите вкладку Ports (Порты). Появится панель «Порты».

Снимите флажок для опции Добавить выходной регистр. Теперь появится панель «Порты», как показано на следующем рисунке.

Выберите вкладку Дополнительно. Появится панель Дополнительно (Advanced).

Выберите параметр Use 'rising _ edge' для регистров. Теперь панель Дополнительно (Advanced) отображается, как показано на следующем рисунке.

Перейдите на вкладку Test stench (Испытательный стенд) в диалоговом окне Generate HDL (Генерировать ЛПВП). В текстовом поле Имя файла замените имя по умолчанию на iir_tb. Этот параметр определяет имя созданного файла тестового стенда.

В диалоговом окне «Создание HDL» нажмите кнопку «Создать» для запуска процесса создания кода. По завершении создания кода нажмите кнопку ОК, чтобы закрыть диалоговое окно.

При создании файлов VHDL фильтра и тестового стенда кодер отображает следующие сообщения в окне команд MATLAB:

### Starting VHDL code generation process for filter: iir ### Starting VHDL code generation process for filter: iir ### Generating: H:\hdlsrc\iir.vhd ### Starting generation of iir VHDL entity ### Starting generation of iir VHDL architecture ### Second-order section, # 1 ### Second-order section, # 2 ### First-order section, # 3 ### HDL latency is 1 samples ### Successful completion of VHDL code generation process for filter: iir ### Starting generation of VHDL Test Bench ### Generating input stimulus ### Done generating input stimulus; length 2172 samples. ### Generating Test bench: H:\hdlsrc\filter_tb.vhd ### Please wait ... ### Done generating VHDL Test Bench ### Starting VHDL code generation process for filter: iir ### Starting VHDL code generation process for filter: iir ### Generating: H:\hdlsrc\iir.vhd ### Starting generation of iir VHDL entity ### Starting generation of iir VHDL architecture ### Second-order section, # 1 ### Second-order section, # 2 ### First-order section, # 3 ### HDL latency is 1 samples ### Successful completion of VHDL code generation process for filter: iir

Как указано в сообщениях, кодер создает папку hdlsrc в текущей рабочей папке и помещает файлы iir.vhd и iir_tb.vhd в этой папке.

Обратите внимание, что сообщения содержат гиперссылки на сгенерированный код и файлы тестового стенда. Щелкнув эти гиперссылки, можно открыть файлы кода непосредственно в редакторе MATLAB.

Созданный код VHDL имеет следующие характеристики:

Объект VHDL с именем iir.

Регистры, использующие асинхронный сброс, когда сигнал сброса является активным высоким (1).

Порты имеют следующие имена по умолчанию:

| Порт VHDL | Имя |

|---|---|

| Вход | filter_in |

| Продукция | filter_out |

| Вход синхросигнала | clk |

| Вход включения тактового синхросигнала | clk_enable |

| Сброс входного сигнала | reset |

Дополнительный регистр для обработки входных данных фильтра.

Входные синхросигналы, входные синхросигналы и порты сброса имеют тип STD_LOGIC а порты ввода и вывода данных имеют тип STD_LOGIC_VECTOR.

Коэффициенты названы coeff, где nn - номер коэффициента, начинающийся с 1.

Представление безопасности типа используется при объединении нулей: '0' & '0'...

Регистры генерируются с помощью rising_edge функция, а не оператор ELSIF clk'event AND clk='1' THEN.

Постфикс '_process' добавляется к именам процессов.

Сформированный испытательный стенд:

Является переносимым файлом VHDL.

Принудительное включение синхросигнала, включение синхросигнала и сброс входных сигналов.

Принудительно переводит входной сигнал включения синхросигнала в активное состояние.

Управляет входным синхросигналом высокой (1) в течение 5 наносекунд и низкой (0) в течение 5 наносекунд.

Инициирует сигнал сброса в течение двух циклов плюс время удержания 2 наносекунды.

Применяет время удержания 2 наносекунды к входным сигналам данных.

Для БИХ-фильтра применяет импульсные, ступенчатые, линейные, чирпические и белые шумовые стимулы.

Ознакомление с сгенерированным кодом VHDL путем открытия и просмотра файла iir.vhd в редакторе симулятора ASCII или HDL.

Открыть созданный файл фильтра VHDL iir.vhd.

Поиск iir. Эта строка идентифицирует модуль VHDL, используя значение, указанное для параметра «Имя» на панели «Цель». См. шаг 2 в разделе Настройка и генерация кода VHDL.

Поиск Tutorial. В этом разделе кодер помещает текст, введенный для параметра Комментарий в заголовке. См. шаг 5 в разделе Конфигурирование и генерация кода VHDL.

Поиск HDL Code. В этом разделе перечислены параметры кодера, измененные при настройке и генерации кода VHDL.

Поиск Filter Settings. В этом разделе кода VHDL описываются настройки конструкции фильтра и квантования, указанные в разделе «Проектирование фильтра IIR» в конструкторе фильтров и «Квантование фильтра IIR».

Поиск ENTITY. Эта строка называет объект VHDL, используя значение, указанное для опции Имя (Name) на панели Цель (Target). См. шаг 2 в разделе Настройка и генерация кода VHDL.

Поиск PORT. Это PORT объявление определяет тактовый сигнал фильтра, включение тактового сигнала, сброс и порты ввода и вывода данных. Порты для синхросигналов, включения синхросигналов, сброса и входных и выходных сигналов данных именуются с использованием символьных векторов по умолчанию.

Поиск CONSTANT. Этот код определяет коэффициенты. Они именуются с использованием схемы именования по умолчанию. coeff_, где xm_sectionnx является a или b, m - номер коэффициента, и n - номер секции.

Поиск SIGNAL. Этот код определяет сигналы фильтра.

Поиск input_reg_process. PROCESS имя блока input_reg_process включает значение по умолчанию PROCESS постфикс блока '_process'. Этот код считывает входной сигнал фильтра из входного регистра. Код для этого регистра создается по умолчанию. На шаге 7 в разделе Configure and Generate VHDL Code (Настройка и генерация кода VHDL) флажок Add output register (Добавить выходной регистр) был снят, но была выбрана опция Add input register (Добавить входной регистр).

Поиск IF reset. Этот код подает сигнал сброса. По умолчанию указан активный высокий (1). Также обратите внимание, что PROCESS применяет стиль асинхронного сброса по умолчанию при генерации кода VHDL для регистров.

Поиск ELSIF. Этот код проверяет растущие границы, когда фильтр работает на регистрах. rising_edge используется, как указано на панели Дополнительно (Advanced) диалогового окна Генерировать ЛПВП (Generate HDL). См. шаг 10 в разделе Конфигурирование и генерация кода VHDL.

Поиск Section 1. В этом разделе данные раздела 1 второго порядка фильтруются. Аналогичные разделы кода VHDL применяются к другому разделу второго порядка и разделу первого порядка.

Поиск filter_out. Этот код управляет выходными данными фильтра.

В этом разделе объясняется, как проверить созданный код VHDL для фильтра IIR с помощью созданного стенда тестирования VHDL. В этом учебном пособии в качестве инструмента для компиляции и моделирования кода VHDL используется симулятор Mentor Graphics ® ModelSim ®. Можно использовать другие пакеты инструментов моделирования HDL.

Чтобы проверить код фильтра, выполните следующие действия.

Запустите симулятор. При запуске симулятора Mentor Graphics ModelSim появляется экран, подобный следующему.

Задайте текущую папку, содержащую созданные файлы VHDL. Например:

cd hdlsrc

При необходимости создайте библиотеку дизайна для хранения скомпилированных объектов VHDL, пакетов, архитектур и конфигураций. В симуляторе Mentor Graphics ModelSim можно создать библиотеку конструкций с помощью vlib команда.

vlib work

Скомпилировать созданные файлы VHDL фильтра и тестового стенда. В симуляторе Mentor Graphics ModelSim выполняется компиляция кода VHDL с помощью vcom команда. Следующие команды компилируют код VHDL тестового стенда фильтра и фильтра.

vcom iir.vhd vcom iir_tb.vhd

На следующем экране отображается последовательность команд и информационные сообщения, отображаемые во время компиляции.

Загрузите стенд для моделирования. Процедура загрузки стенда зависит от используемого тренажера. В симуляторе Mentor Graphics ModelSim загружается тестовый стенд для моделирования с помощью vsim команда. Например:

vsim work.iir_tb

На следующем экране показаны результаты загрузки work.iir_tb с vsim команда.

Откройте окно отображения для мониторинга моделирования при запуске тестового стенда. В симуляторе Mentor Graphics ModelSim используйте следующую команду, чтобы открыть окно волны и просмотреть результаты моделирования как формы сигналов HDL.

add wave *

Появится следующее окно волны.

Чтобы запустить моделирование, выполните команду start simulation для симулятора. Например, в симуляторе Mentor Graphics ModelSim можно запустить моделирование с помощью run команда.

На следующем дисплее показаны run -all используется для запуска моделирования.

Во время моделирования тестового стенда следите за сообщениями об ошибках. Если появляются сообщения об ошибках, интерпретируйте их как относящиеся к конструкции фильтра и выбранным опциям генерации кода HDL. Определите, ожидаются ли результаты на основе настроек, заданных при создании кода фильтра VHDL.

Примечание

Предупреждающие сообщения, которые отмечают Time: 0 ns на предыдущем экране отсутствуют ошибки, и их можно игнорировать.

Сообщение об ошибке, появляющееся на предыдущем экране, не помечает ошибку. Если сообщение содержит текстTest Complete, испытательный стенд был завершен без возникновения ошибки. Failure часть сообщения связана с механизмом, который кодер использует для завершения моделирования.

В следующем волновом окне показаны результаты моделирования в виде сигналов HDL.