Используйте функцию сбора данных FPGA для наблюдения за сигналами от проекта во время его работы на FPGA. Эта функция захватывает окно данных сигнала из FPGA и возвращает данные в MATLAB ® или Simulink ®. Для регистрации сигналов HDL Verifier™ генерирует ядро IP, которое необходимо интегрировать в проект HDL и развернуть в FPGA вместе с остальной частью проекта. HDL Verifier также создает приложение, системную object™ и модель Simulink, которые взаимодействуют с FPGA и возвращают данные в MATLAB или Simulink.

Для сбора данных FPGA:

Создание настраиваемых компонентов и ядра IP. Укажите имена и размеры портов для созданного IP-адреса. Эти порты подключаются к сигналам, которые вы хотите захватить, и сигналам, которые вы хотите использовать в качестве триггеров, чтобы контролировать, когда происходит захват.

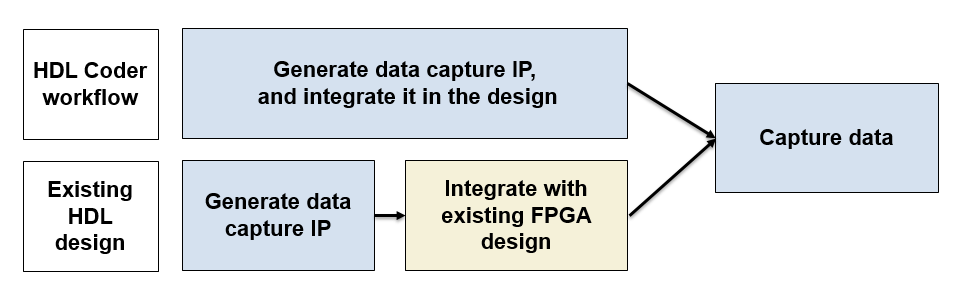

Интеграция сгенерированного IP-адреса в конструкцию FPGA и развертывание конструкции на плате FPGA. Этот шаг автоматизирован при использовании помощника по рабочим процессам HDL.

Используйте созданное приложение, системный объект или модель Simulink для сбора данных для анализа, проверки или отображения. Можно настроить условие триггера для управления при захвате.

Для использования этой функции необходимо загрузить пакет аппаратной поддержки для платы FPGA. Дополнительная документация по этой функции включена в комплект поставки пакета поддержки. См. документацию по пакетам поддержки:

Сбор данных FPGA (пакет поддержки HDL Verifier для системных плат Intel FPGA)

Сбор данных FPGA (пакет поддержки HDL Verifier для плат Xilinx FPGA)

Сведения о загрузке пакетов поддержки см. в разделе Загрузка пакета поддержки платы FPGA.

Высокоуровневый рабочий процесс для сбора сигнальных данных из конструкции, запущенной в FPGA.