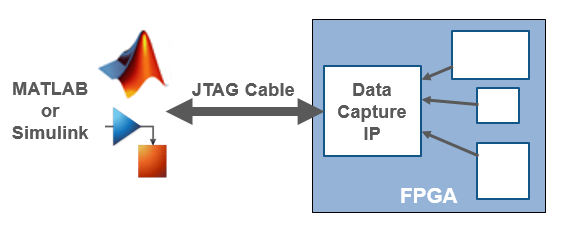

Функция сбора данных FPGA используется для наблюдения за сигналами, поступающими от проекта во время его работы на FPGA. Эта функция захватывает окно данных сигнала из FPGA и возвращает данные в MATLAB ® или Simulink ®.

Для использования этой функции необходимо загрузить пакет аппаратной поддержки для платы FPGA. См. раздел Загрузка пакета поддержки платы FPGA.

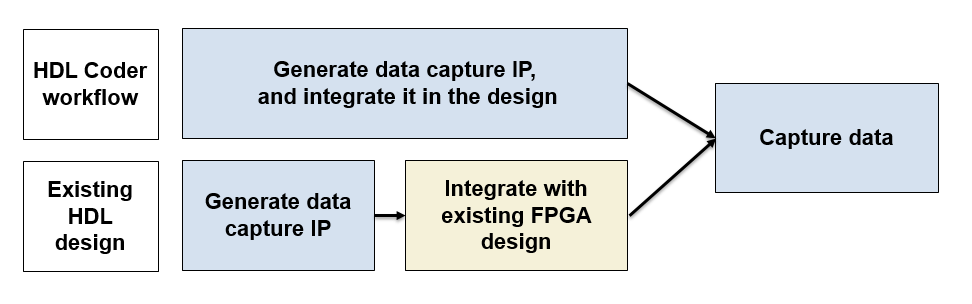

Можно выбрать один из двух рабочих процессов для сбора данных с платы FPGA и возврата их в MATLAB или Simulink.

При создании IP-адреса ЛПВП с помощью Coder™ ЛПВП воспользуйтесь консультантом по рабочим процессам ЛПВП для создания IP-адреса сбора данных и интеграции его в конструкцию FPGA.

При наличии существующей конструкции ЛПВП используйте инструменты Verifier™ ЛПВП для создания IP-адреса сбора данных. Затем вручную интегрируйте сгенерированный IP-адрес в конструкцию FPGA.

Для захвата сигналов из вашей конструкции, HDL Verifier генерирует ядро IP, которое взаимодействует с MATLAB. Используйте рабочий процесс кодера HDL для автоматической интеграции IP-ядра сбора данных в проект. В противном случае вручную интегрируйте это IP-ядро в свой проект HDL и развертывайте его в FPGA вместе с остальной частью проекта. Затем используйте один из этих методов для сбора данных.

Для сбора данных в MATLAB - HDL Verifier генерирует настраиваемое приложение, которое возвращает захваченные данные сигнала. Кроме того, сгенерированный системный object™ можно использовать для программного сбора данных.

Для сбора данных в Simulink - HDL Verifier генерирует блок, имеющий выходные порты, соответствующие захваченным сигналам.

В обоих случаях можно указать типы данных для захваченных данных, количество захватываемых окон и условия запуска, которые управляют выборкой данных.

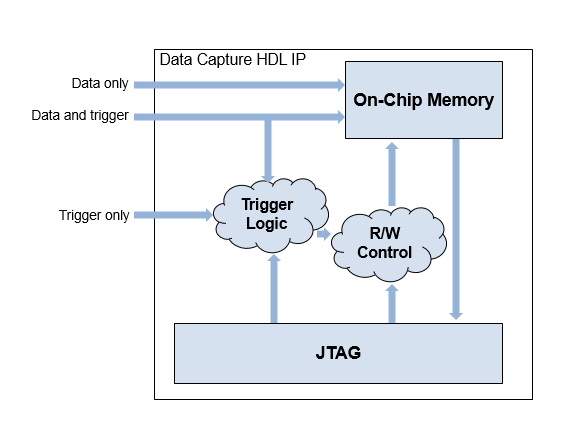

Когда конструкция выполняется на FPGA, сначала генерируемое ядро IP ожидает указанного условия триггера. Определите условие триггера, указав значения, соответствующие одному или нескольким сигналам. При обнаружении триггера логика захватывает назначенные сигналы в буфер и возвращает данные через интерфейс JTAG на хост-машину. Затем эти сигналы можно анализировать и отображать в рабочей области MATLAB или модели Simulink.

При использовании HDL Workflow Advisor для создания конструкции HDL сначала отметьте требуемые сигналы как «Настроить сигналы как контрольные точки» (Simulink) в Simulink. Настройте проект с помощью помощника по рабочим процессам HDL, чтобы:

Включите генерацию тестовых точек, выбрав опцию Enable HDL DUT port generation for test points на шаге Set Target Interface. Дополнительные сведения см. в разделе Установка целевого интерфейса (кодер HDL).

Подключите сигналы контрольных точек к интерфейсу FPGA Data Capture - JTAG на шаге Set Target Interface.

Настройте размер буфера и максимальную глубину последовательности для сбора данных на шаге Создать код RTL и ядро IP. Дополнительные сведения см. в разделе Создание кода RTL и ядра IP (кодера HDL).

Затем выполните оставшиеся шаги для создания HDL для проекта и программирования FPGA. IP-ядро сбора данных интегрировано в сгенерированную конструкцию FPGA. Теперь можно записывать данные из FPGA.

Пример использования сбора данных с помощью HDL Workflow Advisor см. в разделе Отладка IP-ядра с помощью FPGA Data Capture (HDL Coder).

Перед захватом данных FPGA необходимо сначала указать, какие сигналы требуется захватить и сколько выборок данных вернуть. При использовании существующего дизайна HDL используйте приложение FPGA Data Capture Component Generator для настройки параметров и создания IP-ядра захвата данных. Ядро IP содержит:

Порт для каждого сигнала, который требуется захватить или использовать как часть условия триггера

Память для регистрации количества выборок, запрошенных для каждого сигнала

Логика интерфейса JTAG для связи с MATLAB

Логика триггера, которую можно настроить во время выполнения

Приложение также создает настраиваемое приложение FPGA Data Capture, системный объект и модель, которые взаимодействуют с FPGA.

Для взаимодействия MATLAB с FPGA необходимо интегрировать сгенерированное IP-ядро HDL в конструкцию FPGA. Если для создания IP-адреса для сбора данных использовался помощник по документообороту HDL, этот шаг будет автоматизирован, и IP-адрес для сбора данных будет работать с одной тактовой частотой, которая является основным тактовым сигналом тестируемого проекта (DUT). В противном случае следуйте инструкциям в отчете по генерации. Добавление созданных файлов HDL из hdlsrc в проект FPGA. Затем создайте экземпляр IP-ядра HDL, datacapture, в коде HDL и подключите его к сигналам, запрошенным для захвата и триггеров. Скомпилировать проект и запрограммировать FPGA с новым образом. Теперь можно записывать данные из FPGA.

IP-ядро захвата данных FPGA взаимодействует по кабелю JTAG между платой FPGA и хост-компьютером. Убедитесь, что кабель подключен. Перед захватом данных можно задать типы данных для захваченных данных и условия триггера, определяющие время сбора данных. Для настройки этих параметров и сбора данных можно:

Откройте приложение FPGA Data Capture. Установите параметры триггера и типа данных, а затем введите данные в рабочую область MATLAB.

Использовать созданный объект System, полученный из hdlverifier.FPGADataReader. Задайте типы данных и условие запуска с помощью методов и свойств объекта System, а затем вызовите объект для сбора данных.

В Simulink откройте созданную модель и настройте параметры блока FPGA Data Reader. Затем запустите модель для сбора данных.

После ввода данных в рабочую область MATLAB или модель Simulink можно проанализировать, проверить и отобразить данные.