При наличии лицензии Simulink ® Coder™ можно создать тестовый стенд универсальной методики проверки (UVM) и дополнительные компоненты из модели Simulink. Создание компонентов UVM обеспечивает прямой переход от среды Simulink к инфраструктуре UVM.

HDL Verifier™ экспортирует подсистемы Simulink как сгенерированный код C внутри компонентов UVM с прямым интерфейсом программирования (DPI). Эти сгенерированные компоненты можно интегрировать в существующую среду UVM. Можно также использовать созданный стенд тестирования UVM для тестирования HDL DUT путем замены созданного поведенческого DUT детальной конструкцией HDL.

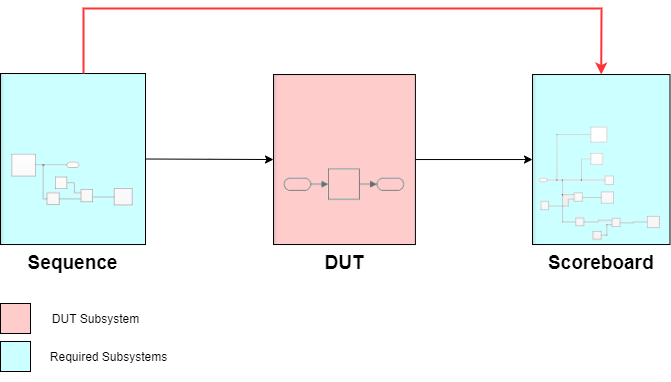

Модель Simulink должна включать эти подсистемы.

Подсистема DUT. Эта подсистема генерирует модель поведения SystemVerilog DPI (SVDPI) для DUT. Дополнительные сведения о создании DPI SystemVerilog см. в разделе Создание компонентов DPI с помощью Simulink.

Подсистема последовательности. Эта подсистема создает стимул и передает его в DUT.

Подсистема табло. Эта подсистема собирает и проверяет выходные данные DUT.

Последовательность также может возбуждать сигналы непосредственно на табло, как показано красным на рисунке Simulink Model Structure.

Дополнительные сведения о создании подсистемы см. в разделе Создание подсистем (Simulink).

Структура модели Simulink

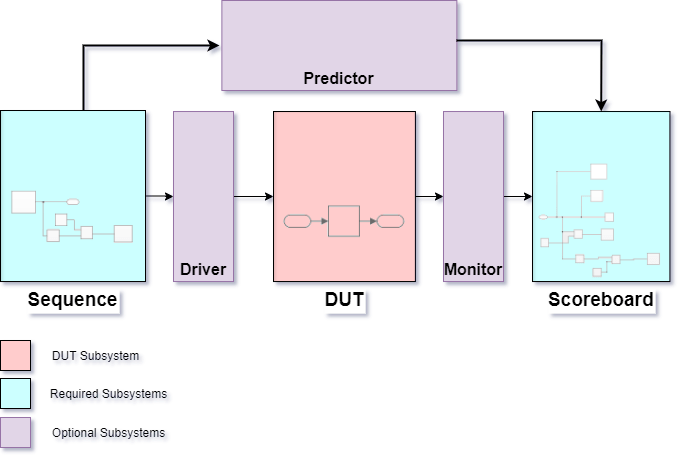

В дополнение к предыдущей структуре можно дополнительно включить эти подсистемы.

Подсистема драйвера

Подсистема мониторинга

Подсистема предиктора

Примечание

Все подсистемы модели Simulink должны иметь имена, начинающиеся с буквы и использующие комбинацию буквенно-цифровых символов и подчеркиваний.

При добавлении монитора, драйвера или подсистемы предиктора эта функция поддерживает эти конфигурации.

Все сигналы, выходящие из последовательности, должны быть соединены с драйвером, предиктором или табло. Другие выходные сигналы игнорируются при формировании UVM.

Если модель включает в себя подсистему драйвера, то все сигналы, поступающие от драйвера, должны быть подключены к DUT.

Если модель включает в себя подсистему драйвера, то все входные сигналы для драйвера должны исходить в последовательности.

Если модель включает подсистему монитора, то все сигналы, поступающие из DUT, должны быть подключены к монитору.

Если модель включает подсистему монитора, то все сигналы, выходящие из монитора, должны быть подключены к табло.

Если модель включает в себя подсистему предиктора, то все входные сигналы для предиктора должны начинаться в последовательности. Дополнительные входные данные игнорируются при формировании UVM.

Если модель включает подсистему предиктора, то все выходные сигналы предиктора должны подключаться к табло. Дополнительные выходы игнорируются при генерации UVM.

На этом рисунке показана модель Simulink, включающая драйвер, монитор и подсистему предиктора.

Поскольку в процессе создания UVM используется технология для создания SystemVerilog DPI, необходимо сначала выбрать поддерживающий целевой файл системы. Откройте диалоговое окно параметров конфигурации и выберите «Создание кода» на левой панели. В поле Системный целевой файл нажмите кнопку Обзор, а затем выберите systemverilog_dpi_grt.tlc из списка.

Кроме того, при наличии продукта Embedded Coder ® можно выбрать целевойsystemverilog_dpi_ert.tlc. Этот целевой объект позволяет получить доступ к дополнительным параметрам создания кода при выборе пункта «Создание кода» на левой панели диалогового окна «Параметры конфигурации».

Пример создания UVM см. в разделе Создание параметризованного испытательного стенда UVM из Simulink.

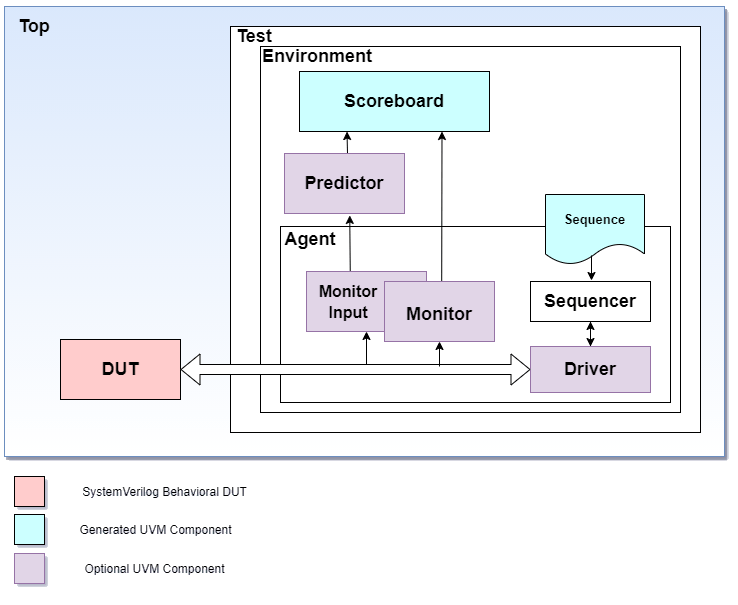

Используйте uvmbuild для создания этой структуры компонентов UVM.

Top - этот модуль создает экземпляр сгенерированного поведенческого DUT и тестовой среды. Верхний модуль имеет сигналы синхронизации и сброса, которые распространяются в конструкцию.

DUT - модуль поведенческого проектирования и тестирования генерируется из подсистемы Simulink DUT.

Тест - этот модуль включает среду UVM и класс последовательности.

Последовательность - этот объект UVM определяет набор транзакций. Объект последовательности генерируется из подсистемы последовательности Simulink.

Среда - этот модуль включает агент и сгенерированное табло, а также дополнительно предиктор.

Табло - табло UVM генерируется из подсистемы табло Simulink. Табло сравнивает ожидаемые результаты с результатами DUT.

Агент - агент UVM включает в себя секвенсор, драйвер и монитор. Если существует прямой путь от подсистемы последовательности Simulink к подсистеме табло Simulink, для контроля этого сигнала включается дополнительный монитор, показанный красным цветом на рисунке.

Sequencer - этот модуль управляет потоком транзакций последовательности в DUT.

Драйвер - этот модуль генерируется из подсистемы драйвера Simulink и преобразует каждую транзакцию из последовательности в сигналы, понятные поведенческому DUT.

Монитор - этот модуль генерируется подсистемой монитора Simulink и выполняет выборку сигналов из поведенческого DUT и генерирует транзакции, отправляемые на табло UVM.

Monitor Input - этот модуль генерируется при наличии предиктора или прямого подключения от последовательности к подсистеме табло. Входной сигнал монитора отбирает сигналы из последовательности и генерирует транзакции, которые посылаются в UVM-предиктор или табло.

Предиктор - этот модуль генерируется из вашей подсистемы предиктора Simulink. Предиктор представляет золотую модель DUT. Он получает входные данные из последовательности, вычисляет результаты и переносит результаты на табло для сравнения с результатами DUT.

Дополнительные сведения о компонентах и структуре UVM см. в справочном руководстве по UVM.

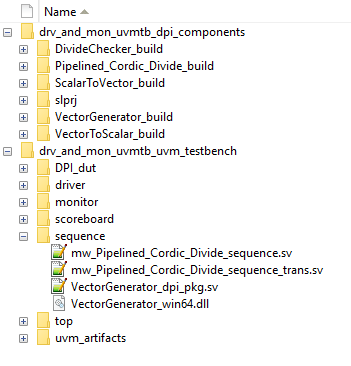

При создании компонентов UVM программа HDL Verifier генерирует компоненты SystemVerilog DPI (SV-DPI) из подсистем DUT, последовательности и табло, а также дополнительные компоненты SV-DPI для подсистем драйвера, монитора или предиктора, если модель их включает. Артефакты создания DPI помещаются в каталог с именем uvm_build в рабочем каталоге, который включает в себя следующие два каталога:

top_model_dpi_components

top_model_uvm_testbench

Где top_modelbuildDirectory свойство в uvmcodegen.uvmconfig объект конфигурации.

top_model_dpi_componentssubsystem_build

subsystem_dpi_pkg.sv

subsystem_dpi.sv

Файлы компонентов DPI и заголовков с расширениями .c и .h

Метаданные и информационные файлы с расширениями .mat, .txt, .dmr, .tmw и .def

Make-файл для компиляции компонентов в файлы .o и .so

top_model_uvm_testbench

DPI_dut - Эта папка содержит копию пакета SystemVerilog, файлы модулей и файл .dll из dut_build

driver (необязательно) - Эта папка создается, если вы указали подсистему драйвера для uvmbuild функция. Эта папка содержит драйвер UVM, копию пакета SystemVerilog и файл общей библиотеки (dll-file или so-file) из driver_build

monitor (необязательно) - Эта папка создается, если вы указали подсистему мониторинга для uvmbuild функция. Эта папка содержит монитор UVM, копию пакета SystemVerilog и файл общей библиотеки (dll-file или so-file) из monitor_build

predictor (необязательно) - эта папка создается, если вы указали подсистему предиктора для uvmbuild функция. Эта папка содержит предиктор UVM, копию пакета SystemVerilog, транзакцию предиктора и файл общей библиотеки (dll-файл или т. д.) из predictor_build

scoreboard - Эта папка содержит копию пакета SystemVerilog и файл .dll из scoreboard_build

sequence - Эта папка содержит копию пакета SystemVerilog и файл .dll из sequence_build

top - Эта папка содержит пакет SystemVerilog и файлы модулей для верхней модели Simulink. Эта папка также содержит сценарии для выполнения HDL-симулятора.

uvm_artifacts - Эта папка содержит эти файлы SystemVerilog.

mw_ - Этот файл включает агент UVM, который создает экземпляр последовательности, драйвера и монитора.DUT_agent.sv

mw_ - Этот файл включает среду UVM, которая создает экземпляр агента и табло.DUT_environment.sv

mw_ - Этот файл определяет тип интерфейса DUT SystemVerilog. Он содержит входы и выходы DUT, а также порты для сигналов синхронизации, сброса и включения синхронизации.DUT_if.sv

mw_ - Этот файл содержит сквозной монитор UVM. Монитор отсчитывает сигналы от драйвера к табло или предиктору.DUT_monitor_input.sv

mw_ - Этот файл включает тест UVM, который создает экземпляр среды и последовательности. Тестовый модуль запускает транзакции путем вызова DUT_test.svseq.start.

mw_dpi_types_pkg.sv - Этот файл содержит определения созданных типов SystemVerilog, таких как enum и struct, предоставляемые интерфейсами компонентов UVM. Этот пакет импортируется только компонентами UVM, использующими эти типы.

mw_ - Этот файл по умолчанию содержит сквозной драйвер UVM. При указании подсистемы драйвера для DUT_driver.svuvmbuild этот модуль включает планировщик и вызовы API к компоненту DPI Driver_dpi_pkg.sv

mw_ - Этот файл содержит сквозной монитор UVM. Монитор производит выборку сигналов от DUT на табло. При указании подсистемы монитора для DUT_monitor.svuvmbuild этот модуль включает планировщик и вызовы API к DPI-компоненту Monitor_dpi_pkg.sv

На этом рисунке показана созданная структура каталогов для модели верхнего уровня с именем drv_and_mon_uvmtb.

Поддерживаемые типы данных Simulink преобразуются в типы данных SystemVerilog, как показано в этой таблице.

Созданные типы SystemVerilog

| MATLAB ® | SystemVerilog | ||

|---|---|---|---|

| Совместимый тип C | Логический вектор | Битовый вектор | |

uint8 | byte unsigned | logic [7:0] | bit [7:0] |

uint16 | shortint unsigned | logic [15:0] | bit [15:0] |

uint32 | int unsigned | logic [31:0] | bit [31:0] |

uint64 | longint unsigned | logic [63:0] | bit [63:0] |

int8 | byte | logic signed [7:0] | bit signed [7:0] |

int16 | shortint | logic signed [15:0] | bit signed [15:0] |

int32 | int | logic signed [31:0] | bit signed [31:0] |

int64 | longint | logic signed [63:0] | bit signed [63:0] |

boolean | byte unsigned | logic [0:0] | bit [0:0] |

| фиксированная точка | Порт имеет расширение на встроенный тип C, например: |

Длина логического вектора ( |

Длина битового вектора ( |

single | shortreal | ||

double | real | ||

complex | Вы можете выбрать между SystemVerilog | ||

| векторы, матрицы | Можно выбрать массивы SystemVerilog или скалярные порты. Чтобы выбрать один из этих параметров, в левой панели диалогового окна Параметры конфигурации выберите Создание кода > SystemVerilog DPI, а затем выберите параметр Scalarize matrix and vector ports. Например, двухэлементный вектор типа input logic [31:0] vecInput [0:1] При выборе Scalarize matrix и vector ports созданный SystemVerilog включает эти два порта, каждый из которых имеет тип input logic [31:0] vecInput_0, input logic [31:0] vecInput_1 При генерации векторных портов и портов массива кодер выравнивает матрицы в порядке «основной столбец». | ||

| невиртуальная шина | Вы можете выбрать между SystemVerilog | ||

| перечислимые типы данных | enum | ||

По умолчанию HDL Verifier преобразует матрицы и векторы в одномерные массивы в SystemVerilog. Например, матрица 4 на 2 в Simulink преобразуется в одномерный массив из восьми элементов в SystemVerilog. Чтобы создать несколько скалярных портов в интерфейсе SystemVerilog, выберите в параметрах конфигурации Scalarize matrix и vector ports.

uvmbuild функция игнорирует компоненты Simulink, которые не указаны как DUT, последовательность, табло, драйвер, монитор или подсистемы предиктора.

Можно использовать петли обратной связи внутри любой из подсистем, но не между ними.

Подсистемы последовательности, табло и предсказателя должны работать с одной скоростью, а время основной выборки их подсистем должно быть равным. Дополнительные сведения о времени образца см. в разделе Время образца в системах (Simulink).

Время основной выборки подсистемы драйвера, DUT и монитора должно быть одинаковым. Их порты могут быть многоскоростными, но время наибольшего общего делителя (GCD) или основной выборки должно быть одинаковым.

Время выборки подсистем последовательности, табло и предиктора должно быть больше или равно времени основной выборки драйвера, DUT и монитора.