Поведенческая модель интегральной схемы драйвера полумоста

Simscape/Электрические/Полупроводники и преобразователи

Блок драйвера полумоста обеспечивает абстрактное представление интегральной схемы для привода полумостов МОП и БТИЗ. Блок моделирует входной гистерезис, задержку распространения и динамику включения/выключения. Если схема драйвера затвора не моделируется явно, всегда используйте этот блок или блок драйвера затвора для установки напряжения источника затвора на блоке MOSFET или напряжения эмиттера затвора на блоке IGBT. Не подключайте управляемый источник напряжения непосредственно к полупроводниковому затвору, так как он пропускает выходной импеданс драйвера затвора, определяющий динамику переключения.

Блок драйвера полумоста имеет два варианта моделирования, доступ к которым можно получить, щелкнув правой кнопкой мыши блок на блок-схеме и выбрав соответствующий параметр в контекстном меню в меню Simscape > Block choices:

Вход PS - состояние выхода драйвера управляется входом физического сигнала u. Используйте этот вариант, если весь контроллер, включая генерацию сигнала PWM, определяется блоками Simulink ®. Этот вариант моделирования используется по умолчанию.

Электрические входные порты - состояние выхода драйвера управляется двумя электрическими входными соединениями, PWM и REF. Этот вариант используется в том случае, если модель имеет аналоговые компоненты восходящего направления, такие как источник управляемого напряжения ШИМ.

Первая пара выходных электрических портов, HO и HS, ведут себя так же, как порты G и S блока драйвера затвора. Подключите эти порты к высокосистемному MOSFET или IGBT полумоста. Вторая пара портов, LO и LS, подключается к низкому MOSFET или IGBT полумоста. Они ведут себя аналогичным образом, за исключением того, что их логика инвертирована относительно логики высокой стороны.

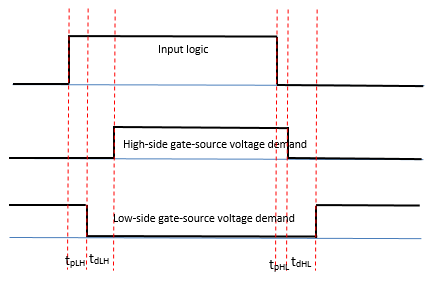

На диаграмме показаны свойства синхронизации для драйвера полумоста, где:

tpLH - задержка распространения на низкой стороне, когда входная логика переходит от 0 к 1.

tdLH - время ожидания на высокой стороне, когда входная логика переходит от 0 к 1.

tpHL - задержка распространения на высокой стороне, когда входная логика переходит от 1 к 0.

tdHL - малое время простоя, когда входная логика переходит от 1 к 0.

Можно вставить ошибку в один или оба выхода в указанное время моделирования. Варианты отказа:

Отказ ввода зафиксирован в логической системе 0

Отказ ввода зафиксирован на логике 1

Отказ с высокой стороны

Неисправная верхняя сторона на

Отказ с низкой стороны

Отказ нижней стороны на

Отказ с высокой и низкой сторон

Отказ на высокой и низкой сторонах

Управляемое напряжение ШИМ | Драйвер литника | N-канальный IGBT | N-канальный MOSFET | P-канал MOSFET