Распространенные шаблоны моделирования, которые приводят к неработоспособной логике в модели, включают в себя:

При выполнении анализа обнаружения ошибок конструкции Simulink ® Design Verifier™ сообщает об общих причинах неработоспособности логики в окне Результаты (Results).

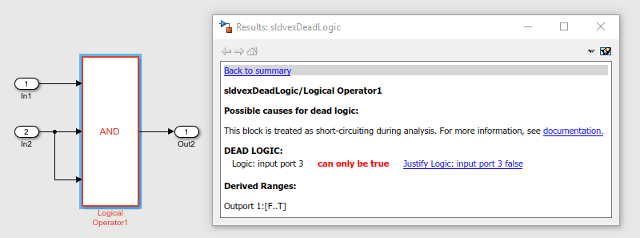

Simulink Design Verifier обрабатывает логические блоки так, как будто они имеют короткое замыкание при анализе неработающей логики.

Например, в этой модели, если In2 false, программа игнорирует третий вход из-за короткого замыкания. В окне Results этот порт отображается как неработоспособная логика. См. раздел Логические операции - короткое замыкание.

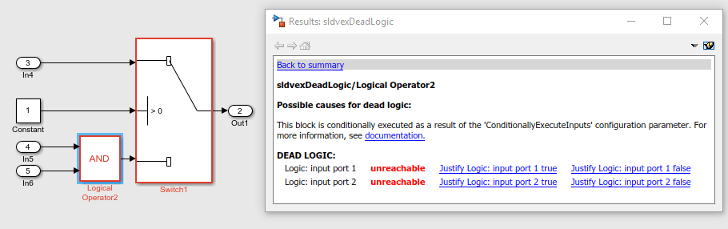

Если модель состоит из блоков Switch или Multiport Switch и параметр выполнения условной входной ветви имеет значение On, условное выполнение часто может вызвать неожиданную мертвую логику.

Рассмотрим пример модели, в которой параметру выполнения условного входного ответвления присвоено значение On. Блок логического оператора И условно выполняется, что вызывает неработоспособную логику для блока. Дополнительные сведения см. в разделе Условное выполнение ветви ввода.

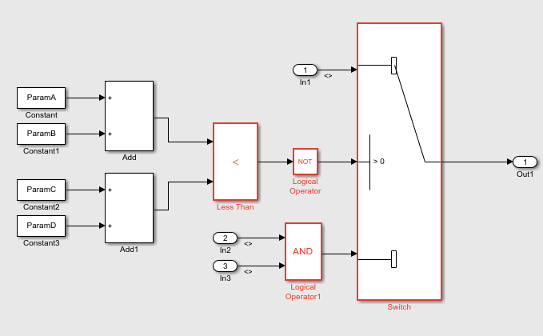

Если модель содержит параметры, Simulink Design Verifier по умолчанию обрабатывает значения как константы. Это может вызвать мертвую логику в модели. В этих случаях рассмотрите возможность настройки этих параметров во время анализа. Дополнительные сведения см. в разделе Встроенные параметры.

Например, рассмотрим эту модель, в которой все параметры равны нулю. Эти настройки вызывают неработоспособную логику для блока «Меньше чем».

Когда конкретный блок имеет мертвую логику, это часто приводит к каскадному эффекту, который приводит к тому, что дочерние блоки имеют мертвую логику.

Рассмотрим приведенный выше пример модели. Мертвая логика в блоке Меньше Чем вызывает мертвую логику в соответствующих нисходящих блоках. Поэтому часто бывает полезно просмотреть логику нечувствительности восходящего потока, прежде чем рассматривать любую логику нечувствительности нисходящего потока.

Библиотечные блоки могут быть записаны с защитными условиями, которые являются избыточными в некоторых местах, где они используются. В некоторых случаях это может вызвать мертвую логику. См. раздел Исключение и выравнивание целей для обнаружения ошибок конструкции.

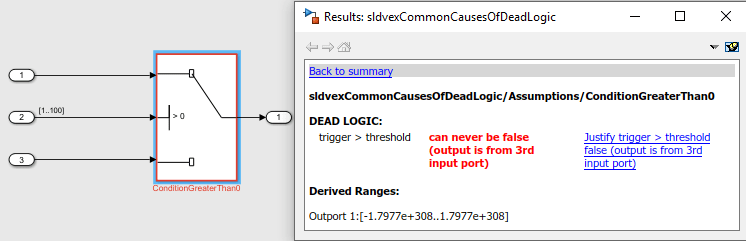

Блоки ввода корневого уровня с минимальными и максимальными значениями в качестве ограничений и блоки тестовых условий в тестовой генерации могут вызывать неработоспособность логики. Например, рассмотрим блок ConditionGreaterThan0 Switch, где второй блок Inport имеет минимальный и максимальный диапазоны 1 и 100 соответственно. Это приводит к тому, что блок коммутатора в этой подсистеме имеет неработоспособную логику.